# **Revision Control Methodology**

Presented By

Brian Lay

Product Marketing Manager

10/2/2018

## **Agenda**

- > Motivation

- > Recommendations for implementing a revision control strategy

- >> RTL projects

- >> IP projects

- >> BD projects

- > Future improvements

## Importance of Maintaining a Revision Control Strategy

- > Reproduce previous results

- > Board revisions

- > Co-development

- > Compliance

- > Revenue

# Implementing a Revision Control Strategy

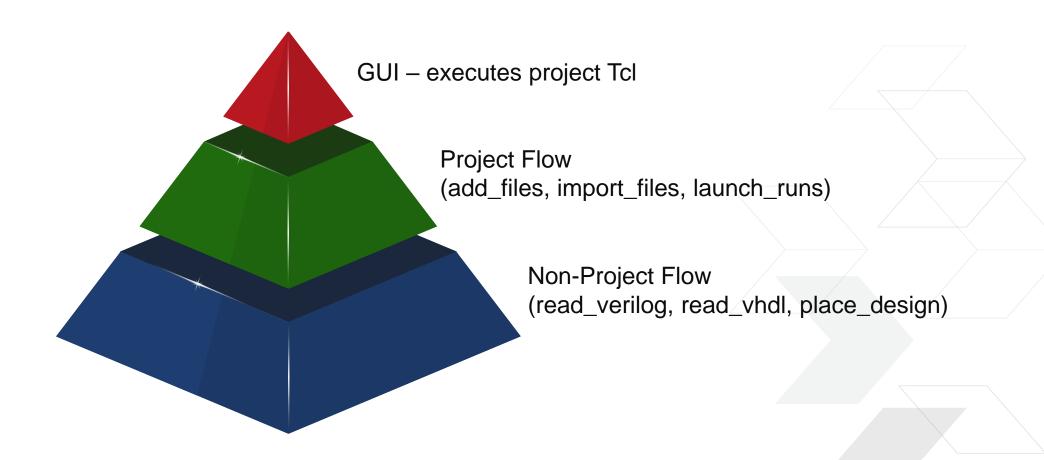

#### **Foundations of Vivado**

Focusing on project based scripted flow

#### Strategy for Successful Revision Control

- > Use scripted flows for revision control

- > Keep sources external to the project

- > Revision control the source repository

- > Generate a script to recreate the project

- > Revision control the script

- > Test your methodology

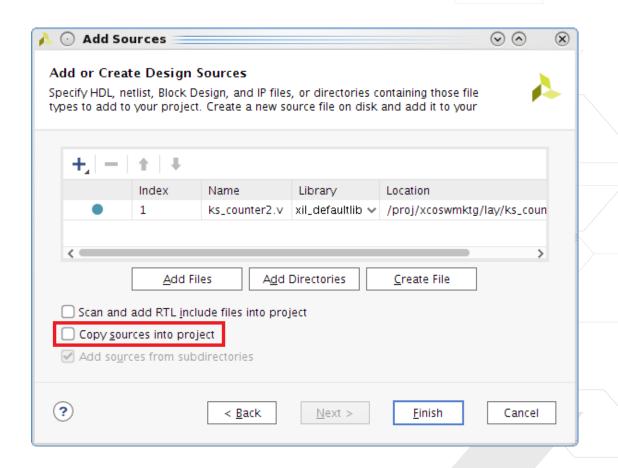

#### **Adding Sources to Projects**

- > Use add\_files for all sources

- >> Keeps sources external to the project

- >> Un-check "Copy sources into project"

- > Filesets contain all project sources

- >> get\_filesets

- >> Four "default" filesets

- >> get\_files -of [get\_filesets]

#### RTL Example

./userdir ./my\_repo/2018.2 ./workspace

./my\_repo/2018.2

bft.vhdl

FifoBuffer.v

async\_fifo.v

bft\_package.vhdl

core\_transform.vhdl

round\_1.vhdl

round\_2.vhdl

round\_3.vhdl

round\_4.vhdl

bft\_full.xdc

build.tcl

#### build.tcl

launch runs impl 1 - jobs 8

```

set dirname project foo

create project $dirname . -part xc7k70tfbg484-2

set source repo ../my repo/2018.2

add_files $source_repo/bft.vhdl

add files $source repo/FifoBuffer.v

add files $source repo/async fifo.v

add files $source repo/bft package.vhdl

add files $source repo/core transform.vhdl

add files $source repo/round 1.vhdl

add files $source repo/round 2.vhdl

add files $source repo/round 3.vhdl

add files $source repo/round 4.vhdl

add files -fileset constrs 1 $source repo/bft full.xdc

set property library bftLib [get files $source repo/round 1.vhdl]

set property library bftLib [get files $source repo/round 2.vhdl]

set property library bftLib [get files $source repo/round 3.vhdl]

set property library bftLib [get files $source repo/round 4.vhdl]

set property library bftLib [get files $source repo/core transform.vhdl]

set property library bftLib [get files $source repo/bft package.vhdl]

set_property top bft [current fileset]

update compile order -fileset sources 1

```

vivado -source ../my\_repo/build.tcl

### **Creating a Project Script**

- > Manually create the script

- >> Minimalist

- Organized

- >> Risk missing some settings

- > Automatically create the script using write\_project\_tcl

- >> Verbose

- Complicated

- >> Robust, should not miss any settings

- > Scripts must be maintained as projects evolve

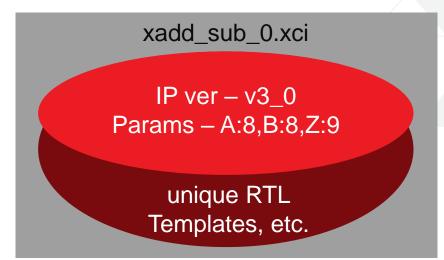

## **Understanding Xilinx IP**

Xilinx IP Repository vivado/<version>/data/ip/xilinx/

xadd\_sub\_v3\_0

component.xml RTL with parameters constraints, etc.

2018.1

Workspace

IP ver - v3\_0

Params - A:8,B:8,Z:9

unique RTL

Templates, etc.

Source Repo

build.tcl xadd\_sub\_0/ xadd\_sub\_0.xci .ignore

xadd\_sub\_v4\_0

component.xml RTL with parameters constraints, etc.

2018.2

build.tcl xadd\_sub\_0/ xadd\_sub\_0.xci

Upgrade to v4\_0

#### **Xilinx IP Revision Control Options**

| <b>IP Files to Revision Control</b> | Size | Compile time      | Re-customizable <sup>1</sup> | Forced to upgrade <sup>2</sup> |

|-------------------------------------|------|-------------------|------------------------------|--------------------------------|

| XCI                                 | S    | Slow <sup>3</sup> | Υ                            | Υ                              |

| TCL (write_ip_tcl)                  | S    | Slow <sup>3</sup> | Υ                            | Υ                              |

| Whole IP directory                  | L    | Fast              | Υ                            | N / locked                     |

| XCIX                                | M    | Fast              | Υ                            | N / locked                     |

| DCP                                 | S    | Fast              | N                            | NA                             |

#### > Two real options

>> XCI or XCIX

#### > Recommendation

- Start with only the XCI file

- >> On upgrade switch to XCIX for IP with changes that are too disruptive

<sup>&</sup>lt;sup>1</sup> In the existing version of Vivado that generated the original XCI

<sup>&</sup>lt;sup>2</sup> Rebuild project using the existing version of Vivado and open project with latest version

<sup>3</sup> With Out-of-context synthesis and IP caching on a legisle time differences may be negligible

## **Avoid Using the DCP**

- > A DCP generated out-of-context (OOC) is unconstrained

- > IP are synthesized OOC

- > Scoped timing constraints are used during the OOC synthesis run

- > Timing constraints are discarded prior to writing the DCP

- > Using the XCI or XCIX files ensure a fully constrained design

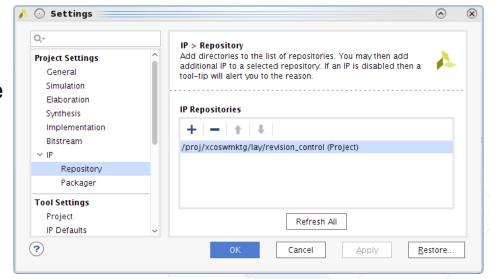

#### Managing Custom IP Using Repositories

- > Develop IP in a revision controlled working directory

- > Package the IP into a custom IP repository

- >> Follow Xilinx IP repository directory structure as a reference

- >> <vivado\_version>/data/ip/<company>/<IPname\_version>

- > Working project directories

- Set IP repository path

- >> Add XCI

- >> Add both to the build script

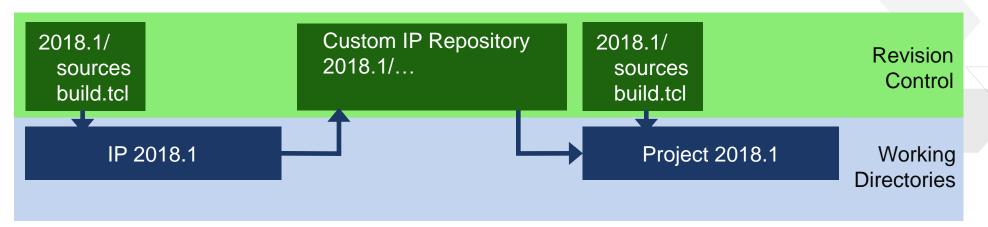

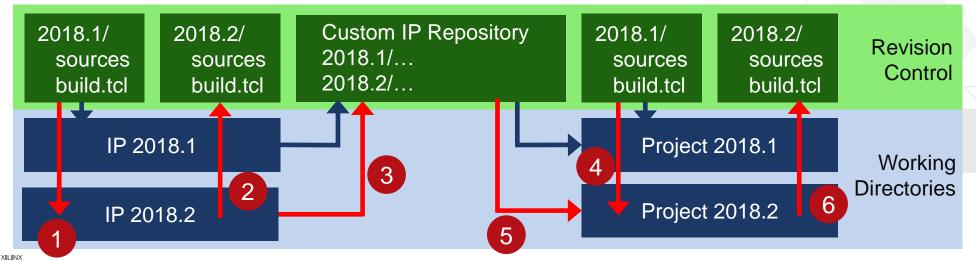

## Upgrading Custom IP (using Xilinx IP) Repositories

- 1. Create new IP directory from previous sources

- 2. Upgrade project and check in new IP files

- 3. Re-package all IP into new custom <vivado\_version> repository

- 4. Rebuild project directory from previous sources

- 5. Update the IP repository

- 6. Upgrade project and check in new project files to repository

### Propagation of Parameters in Block Designs

Xilinx IP Repository vivado/<version>/data/ip/xilinx/

v\_hdmi\_tx\_ss\_0\_v2

component.xml RTL with parameters constraints, etc.

2018.1

Workspace

design\_1.bd

IP\_ver = \_v2

Non-default IP params

XCI name for each instance

Propagate parameters

Identify conflicts

Update XCI / BD

unique RTL for BD/IP, etc.

v\_hdmi\_tx\_ss\_0\_v3

component.xml RTL with parameters constraints, etc.

2018.2

design\_1.bd

IP\_ver = \_v2

Non-default IP params

XCI name for each instance

\_v2

Upgrade to V3

Source Repo

build.tcl design\_1/ design\_1.bd .ignore

build.tcl

design\_1/

design\_1.bd

ip/

v\_hdmi...\_v2/\*

.ignore

## **Preserving Block Designs**

| BD file to revision control | Size | Compile time      | Preserve Layout       | Forced to upgrade |

|-----------------------------|------|-------------------|-----------------------|-------------------|

| BD                          | S    | Slow <sup>1</sup> | $N^2$                 | <b>Y</b> 3        |

| TCL (write_bd_tcl)          | S    | Slow <sup>1</sup> | <b>Y</b> <sup>4</sup> | Υ                 |

| Whole BD directory          | L    | Fast              | Υ                     | N / locked        |

#### > Recommendation

- >> Use write\_bd\_tcl to preserve entire BD including layout

- >> If you want selective IP upgrade, then move towards BD

<sup>&</sup>lt;sup>1</sup> With Out-of-context synthesis and IP caching enabled, compile time differences may be negligible

<sup>&</sup>lt;sup>2</sup> Can be preserved by checking the BD/ui directory

<sup>&</sup>lt;sup>3</sup> Not with selective IP upgrade. Generated output products of IP still need to be preserved

<sup>4</sup> Use \_include\_layout flag. © Copyright 2018 Xilinx

<sup>&</sup>lt;sup>4</sup> Use -include\_layout flag

#### **Additional Files to Revision Control**

#### > Other source files

- >> XDC

- >> Simulation test benches

- Sysgen IP

- >> HLS IP

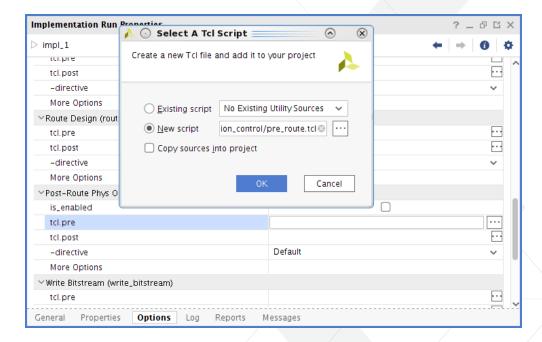

- >> Pre/post tcl scripts

- >> Incremental compile DCPs

- >> ELF files

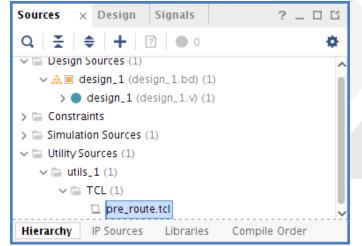

#### > Util\_1 source set introduced in 2018.1

- >> Files are now managed by the project

- >> Included in a project archive

#### **Output Files to Consider for Revision Control**

- > Simulation scripts for 3<sup>rd</sup> party simulators (export\_simulation)

- > Hardware definition files for SDK (export\_hardware)

- > DSAs for export to SDx (write\_dsa)

- > Bitstreams (generate\_bitstream)

- > Hardware debug (.ltx, .lpr, debug dashboards)

- > Intermediate run results (runs / checkpoints)

#### **Future Revision Control Improvements**

- > Auto create .ignore files

- > Separate output products from the sources

- > Make the BD the one true source for a design

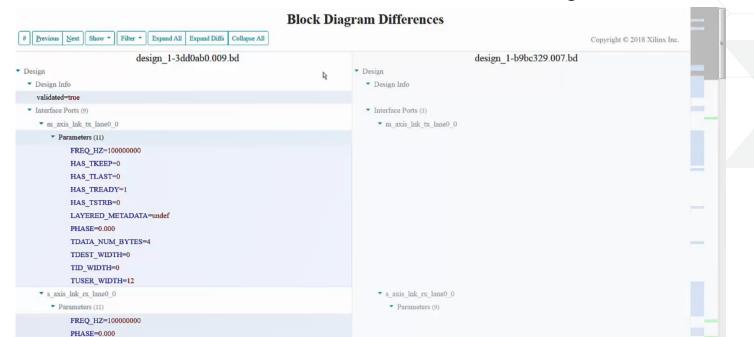

- > BD Differences

- >> Compare two BD to understand the differences between the designs

#### Summary

- > Vivado provides the frameworks to develop your revision control strategy

- > Six general steps

- >> Use scripted flows for revision control

- >> Keep source files in a repository

- >> Revision control the repository

- >> Create a Tcl script to recreate the project

- >> Revision control the script

- >> Test your scripts