ISSUE 87, SECOND QUARTER 2014

SOLUTIONS FOR P R O G R A M M A B L E WORLD А

SYSTEM ARCHITECT

IMPLEMENTATION ENGINEER

SOFTLY DEFINED LINE CARD

## **Xilinx's SDNet Enables** 'Softly' Defined Networks

VIVADO.

UltraScale Architecture Advances Wireless Radio Applications

How to Use Interrupts on the Zyng SoC **Xilinx Opens a Tcl Store** What's New in Vivado 2014.1?

ALL PROGRAMMABLE FPGA OR SOC

**Motor Drives** Migrate to Zyng SoC with Help from 32 MATLAB

SDNet

Environment

www.xilinx.com/xcell

## Xilinx<sup>®</sup> SpeedWay Design Workshops<sup>™</sup>

### Featuring MicroZed<sup>™</sup>, ZedBoard<sup>™</sup> & the Vivado<sup>®</sup> Design Suite

Avnet Electronics Marketing introduces a new global series of Xilinx<sup>®</sup> SpeedWay Design Workshops<sup>™</sup> for designers of electronic applications based on the Xilinx Zynq<sup>®</sup>-7000 All Programmable (AP) SoC Architecture. Taught by Avnet technical experts, these one-day workshops combine informative presentations with hands-on labs, featuring the ZedBoard<sup>™</sup> and MicroZed<sup>™</sup> development platforms. Don't miss this opportunity to gain hands-on experience with development tools and design techniques that can accelerate development of your next design.

em.avnet.com/xilinxspeedways

DESIGNED BY AVNET

### Announcing HAPS Developer eXpress Solution

Pre-integrated hardware and software for fast prototyping of complex IP systems

Designs come in all sizes. Choose a prototyping system that does too. HAPS-DX, an extension of Synopsys' HAPS-70 FPGA-based prototyping product line, speeds prototype bring-up and streamlines the integration of IP blocks into an SoC prototype.

To learn more about Synopsys FPGA-based prototyping systems, visit www.synopsys.com/haps

www.xilinx.com/xcell/

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 www.xilinx.com/xcell/

© 2014 Xilinx, Inc. All rights reserved. XILINX, the Xilinx Lago, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any daim it might have against Xilinx for any loss, damage, or expense caused thereby.

### Here's to 30 Years of Innovation and to Many Decades More

ilinx celebrated its 30th anniversary in February. As someone who is a relative newcomer, having joined the company in 2008, I find it remarkable how far and fast Xilinx and the devices we make have advanced in just the last six years. I can't imagine what it must be like for the employees who have been with the company essentially from the beginning, when Xilinx was a tiny startup on Hamilton Avenue in San Jose offering what to many seemed like a crazy technology with an even crazier business model.

FPGAs and the fabless semiconductor business model are mainstays of the industry today, but back in 1984 that wasn't the case. Years ago, I had the pleasure of interviewing Bill Carter, who in the Xilinx world is a bit of a living legend, having laid out the industry's very first FPGA, the XC2064, and later becoming Xilinx's first CTO. Of the many great recollections Bill shared regarding his years at Xilinx, one of the most memorable was the story of his job interview with Xilinx's co-founders: Ross Freeman (who invented the FPGA), Bernie Vonderschmitt and Jim Barnett. Basically, the founders laid out their plans to come up with a reprogrammable device and have it manufactured by Seiko-Epson.

"I took one look at the architecture and thought they were nuts," said Carter. "Back then, silicon real estate was precious and their new circuit structure took so many transistors to implement. But the idea of being able to reprogram the hardware was revolutionary."

The business model was sort of nuts too for that time. Back in 1984, everyone manufactured their own chips and the biggest barrier to entry into the business was securing enough funding to build a factory. Carter recalled that Vonderschmitt knew manufacturing from his days at RCA and could call on his friends at Seiko (to whom he had shown the silicon-manufacturing ropes while working at RCA) to produce the chips.

So here was Bill Carter, with a young family and a mortgage to pay, working a solid job for established Zilog, creator of the Z80. He walked away to take a chance with Xilinx. The rest is history. Xilinx introduced FPGAs to the world in 1985, and years later the fabless model under the leadership of TSMC became the mainstream way to produce chips.

What I realize 30 years after the fact is that while many personalities have come and gone and shaped the character of Xilinx, the risk-taking, innovative spirit that launched the company is still thriving here. In the last six years, I've been an eyewitness to Xilinx gaining a Generation Ahead lead over the competition at the 28-nanometer node by means of innovative silicon (7 series All Programmable FPGAs, SoCs and 3D ICs) and tools (the Vivado<sup>®</sup> Design Suite). What's more, Xilinx is stretching that lead with first-to-market 20-nm UltraScale<sup>TM</sup> devices. And you can count on even bigger innovations coming down the pike as the era of the FinFET arrives. This pioneering spirit is charged by the remarkable innovations Xilinx customers have created with our chips over the last 30 years. I'm sure we'll see even more customer innovations in the decades ahead.

Editor's Note: If you are interested in reading about the early pioneering years of Xilinx and the fabless industry, I recommend this great piece, "Xilinx and the Birth of the Fabless Semiconductor Industry," written by Xcell Daily's editor, Steve Leibson. If you want to keep up to date with the future Xilinx innovations, please keep reading and contributing great technical content to Xcell Journal—now proudly in our 26th year of publishing.

Mike Santarini Publisher

# Xcell Journal Adds New Daily Blog

Xilinx has extended the Award Winning Journal and added an exciting new *Xcell Daily* Blog. The new site provides dedicated readers with a frequent flow of content to help engineers leverage the flexibility and extensive capabilities of Xilinx products, ecosystem, and customers to create All Programmable and Smarter Systems.

-ellda

SOLUTIONS FOR A PROGRAMMABLE WORLD

Nushed a blog cost on the Semi-Wild site that describes

A Similar the year of the state of the state of the

internation or limber (a) and not base to run

#### Recent

Leig Contra

Is DDR4 the last SDRAM protocol? Yes, says SemiWiki's Eric Esteve. Then what are the alternatives?

Using Vivado HLS, the FPGA Expert creates pipelined FPU with 18

lines of C code in 10 minutes, including diaper change

- Access memory-mapped devices in Linux without writing drivers on the Zyng<sup>®</sup>-based ZedBoard

- Jan Gray's New LUT Math: How many 32-bit RISC CPUs fit in an FPGA? Now vs. 1995?

- For Zyng SoC Developers: Latest version of ARM<sup>®</sup> Cortex<sup>™</sup>-A Programmer's Guide just published. Download now!

- XIMEA CB200 5K digital video camera pumps 1.7Gbytes/sec down a 300M optical cable using FPGA-based PCIe

Visit Blog: www.forums.xilinx.com/t5/Xcell-Daily/bg-p/Xcell

Using Vivado HLS, the FPGA Expert

Analog Gewons and Xulinx damor

Such members of the Zyna A

#### $\mathsf{C} \ \mathsf{O} \ \mathsf{N} \ \mathsf{T} \ \mathsf{E} \ \mathsf{N} \ \mathsf{T} \ \mathsf{S}$

#### VIEWPOINTS

#### Letter From the Publisher

Here's to 30 Years of Innovation and to Many Decades More... **4**

#### XCELLENCE BY DESIGN APPLICATION FEATURES

#### **Xcellence in Wireless**

Xilinx's 20-nm UltraScale Architecture Advances Wireless Radio Applications...**14**

#### **Xcellence in Industrial**

Angle Measurement Made Easy with Xilinx FPGAs and a Resolver-to-Digital Converter...**24**

#### **Xcellence in Industrial**

Motor Drives Migrate to Zynq SoC with Help from MATLAB...**32**

## **Cover Story**

Invironmen

VIVADO

8

Xilinx's New SDNet Environment Enables 'Softly' Defined Networks

SYSTEM ARCHITECT

ALL PROGRAMMABLE

32

#### THE XILINX XPERIENCE FEATURES

#### **Xplanation: FPGA 101**

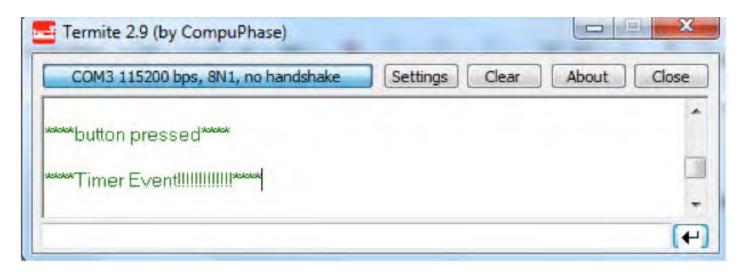

How to Use Interrupts on the Zynq SoC... **38**

#### **Xplanation: FPGA 101**

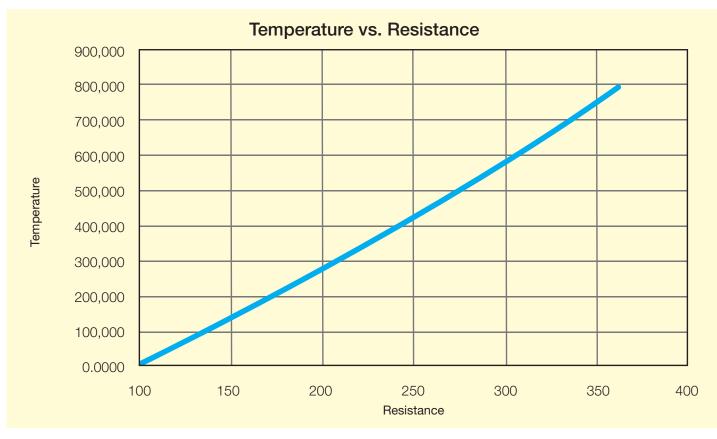

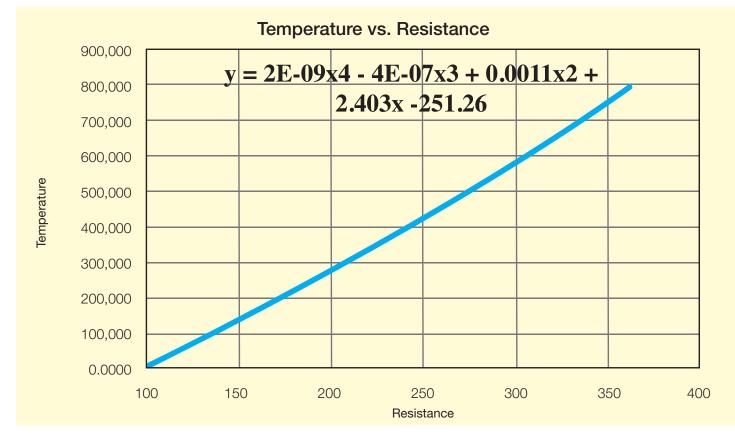

Calculating Mathematically Complex Functions... **44**

#### **Xplanation: FPGA 101**

Make Slow Software Run Fast with Vivado HLS... **50**

#### **Tools of Xcellence**

Xilinx Opens a Tcl Store... 54

#### XTRA READING

**Xtra, Xtra** The latest Xilinx tool updates and patches, as of April 2014... **60**

**Xpedite** Latest and greatest from the Xilinx Alliance Program partners... **62**

**Xamples** A mix of new and popular application notes... **64**

**Xclamations** Share your wit and wisdom by supplying a caption for our wild and wacky artwork... **66**

#### COVER STORY

## Xilinx's New SDNet Environment Enables 'Softly' Defined Networks

VIVADOA

IMPLEMENTATION ENGINEER

With Xilinx technology, design teams can now build a line card on a chip and tailor their hardware for specific network services and applications.

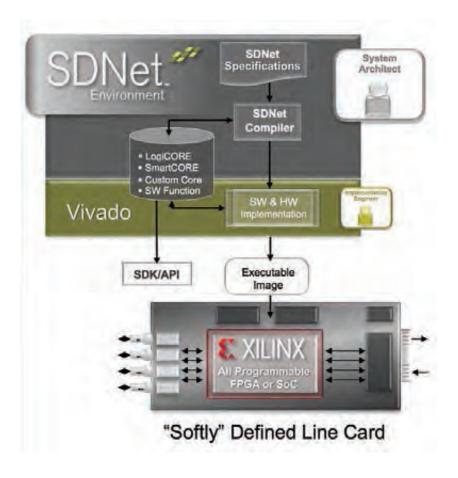

At a time when communications architectures are rapidly evolving, driven by consumer demand for greater bandwidth and better, more reliable and secure services, Xilinx has innovated a game-changing technology and design approach that will enable its customers to quickly produce and upgrade next-generation line cards for wired and wireless networks as well as data centers. The new technology is SDNet, a software-defined specification environment. When used with Xilinx<sup>®</sup> All Programmable FPGAs and SoCs, SDNet allows communications design groups to apply a revolutionary approach that Xilinx calls "Softly" Defined Networks to the design and upgrade of line cards for the next generation of software-defined network architectures.

#### FROM FIXED NETWORKS TO SDN

The communications architectures of the past 20 years have mainly comprised fixed control and data planes that didn't expand as network requirements evolved, said Nick Possley, vice president of communications IP and services at Xilinx. This rigid architecture required carriers to replace equipment frequently if they wanted to expand network functionality and increase overall bandwidth. The line cards at the heart of these systems were largely based on a mix of highly specialized ASICs, ASSPs and memory ICs. FPGAs served to accelerate and bridge communications among the chips on the line card.

As the pace of demand quickened, carriers and the communications systems companies that serve them sought better alternatives. In the last few years, they have turned to software-defined networks (SDN) and network functions virtualization (NFV). These architectures separate the control and data planes, and add more software virtualization to the control Software-Defined Networks

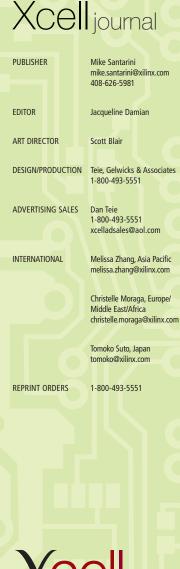

Figure 1 – Today's software-defined networks separate the control and data planes but still have fixed data planes, minimal differentiation and short life cycles.

plane. As a result, carriers can rapidly deploy new applications, and network equipment is easier to upgrade than in traditional networks. This improves longevity (and profitability) and simplifies network management (Figure 1).

But Possley said that even the most recent SDN and NFV architectures are too rigid in that the data planes are not programmable and the designs typically are based on off-the-shelf ASSPs. The line cards at the heart of the network use discrete off-the-shelf packet-processor and traffic-manager ASSPs connected to optics, along with coprocessors and external memory. The cards also include FPGAs to accelerate communications among all of these chips.

The latest versions of ASSPs that various chip makers have created for SDN and NFV architectures do comply with SDN specifications. But because the suppliers make the same ASSPs generally available to all network systems companies, these chips provide no competitive product differentiation or feature expansion. As a result, network system vendors are forced to compete on lowest pricing to carriers.

On the surface, one would think the carriers would love this lower equipment pricing. But in reality, fixed data-plane designs even in ASSP-based SDN architectures are still so rigid that carriers will have to make expensive in-field line-card swaps when they find out the ASSP's fixed hardware functionality can't accommodate ever-changing applications, protocol updates and new feature requirements. These line-card swaps require networks to shut down while technicians remove obsolete cards and install new ones. What's more, ASSP vendors tend to overbuild the functionality of their designs in an attempt to address a broad number of markets with a single device. As a result, these ASSP-based line cards tend to be power hungry and thus run hot, so carriers must take extra measures to keep the equipment cool. The cost of cooling, of course, adversely affects operating expenditures and further cuts into a carrier's bottom-line profitability.

#### A BETTER SOLUTION: SOFTLY DEFINED NETWORKS

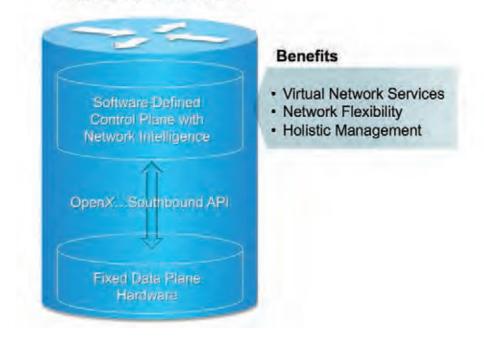

With SDNet and Xilinx's revolutionary softly defined network approach, communications systems companies can develop integrated, low-power, All Programmable line cards that boast far more than a software-defined control plane with network intelligence required by SDN architectures. This new technology will also let vendors differentiate their systems with software-defined data-plane hardware that has content intelligence, meaning that design teams can tailor the hardware to the exact network services and applications their systems require (Figure 2).

Traditionally, network architects (who typically don't have hardware design backgrounds) express the requirements of particular protocols in English-language descriptions, such as Internet requests for comment (RFCs) or ISO standards documents.

They then have to rely on specialized engineers who are very well-versed in the underlying architecture of the target device to manually turn those requirements into low-level, implementation-specific, descriptions (typically using highly specialized microcode). These hardware engineers will either specify how the general-purpose processors or specialized network processors should perform the packet processing, or they will design the functionality into a custom ASIC.

Network design teams then have to verify that hardware achieves the architect's original design intent or can at least accommodate the most recent version of the protocol they intend the card to use. If the line card doesn't meet the requirements, they have to repeat the design process until they get it to work properly. This process is complicated by the fact that the relationship between the desired specification and the microcode is not intuitive and the underlying architecture has performance limitations and capabilities that vary based on the services companies are targeting.

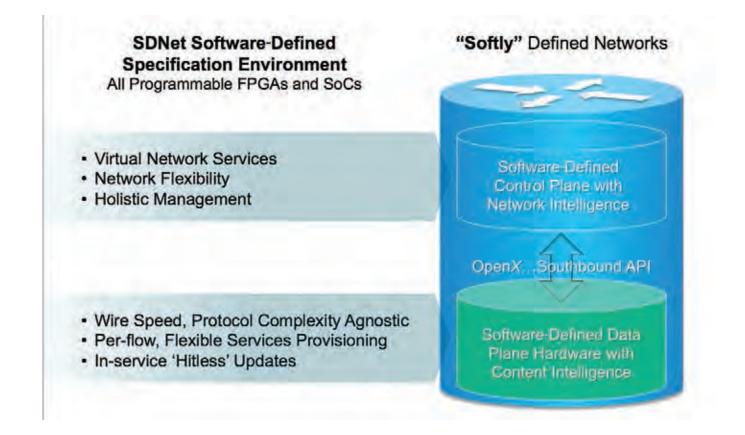

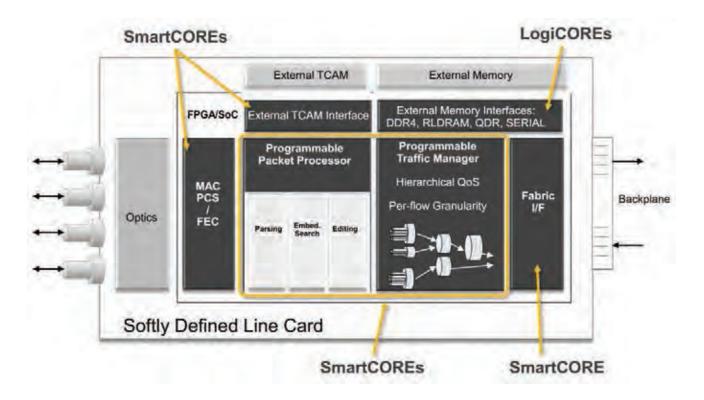

SDNet's softly defined network approach goes to the root of this problem and allows network system design teams to quickly design line cards that are correct by construction. In particular, SDNet focuses on automating the most complex aspect of line card design—namely, the design and programming of the packet-processor and traffic-manager functions in modern line cards (Figure 3).

Instead of having two separate, discrete ASSPs handling these functions, network systems teams can integrate packet processing and traffic management as well as other line card functionality on a single Xilinx All Programmable FPGA or SoC. They can ensure they are creating optimal implementations for their targeted applications. In addition to integrating the functionality of many chips into one All Programmable device, SDNet streamlines the creation of a high-level behavioral specification of the line card and automatically generates RTL blocks for implementation in Xilinx All Programmable devices, firmware and a validation testbench.

"With SDNet, system architects specify the 'what,' not the 'how," said Possley. "System architects specify the exact services they are looking to deploy without regard as to how they are being deployed in the underlying silicon."

In the SDNet flow, system architects define line-card functionality using a high-level functional specification (Figure 4). SDNet allows architects to describe the required behavior of various types of packet-processing engines, including parsing, editing, search and quality-of-service (QoS) policy engines. Architects can describe engines hierarchically in terms of simpler subengines that they can interconnect and arrange into packet data flows. These subengines can include user-provided engines. The SDNet specification environment contains no implementation details. That gives customers the freedom to scale the performance and resources of their design without the need to understand the details of the underlying architecture. The SDNet specifications are also not limited to any specific network protocols.

Possley said that SDNet is simple, and the select few customers with whom Xilinx beta tested it have found it very intuitive and easy to use. "It dramatically cuts the amount of code they have to produce into a simple and intuitive specification and is, therefore, orders-of-magnitude less effort compared with microcoding a network processor," he said.

Once architects have finished defining the system engines and flows in the SD-

Figure 2 – SDNet brings flexibility and automation to the data plane, enabling a softly defined network approach for the design and upgrade of next-generation networks.

Figure 3 – With SDNet, companies can create a highly integrated All Programmable line cards.

Net specification environment, they provide SDNet's compiler with throughput and latency requirements and run-time programmability requirements that influence the optimized hardware architecture generated by the compiler. They then execute a command, and SDNet's compiler automatically generates the RTL for the hardware blocks the design requires. The compiler also generates firmware and a verification/validation testbench. The SD-Net design environment includes integration of Xilinx-optimized SmartCOREs for networking and LogiCOREs<sup>TM</sup> for connectivity, external memory control and embedded processors.

After compilation, network engineers can then finish the implementation of the design in the Vivado<sup>®</sup> Design Suite using the IP Integrator (IPI) tool. They first use the Vivado tools and IPI to transform the RTL architecture description the SDNet compiler has generated into an optimized Xilinx FPGA implementation. They can then integrate any additional line-card functionality into the FPGA, given sufficient resources on the device they've selected, essentially

Figure 4 – The SDNet-based implementation flow enables correct-by-construction design of an All Programmable line card.

creating an All Programmable line card on a chip.

What's more, SDNet generates data for functional verification and validation to guide correct-by-construction design. Specifically, SDNet's compiler accepts a collection of test packets for testing input and output of the design. Architects can use the packets in the specification-definition phase of the process to ensure they are creating an accurate interpretation of the SDNet description. Network engineers can use test packets during the simulation of the RTL description generated by the SDNet compiler. Last but not least, the packets can help with hardware validation of the final implementation of the design using network test equipment. In addition, SDNet will generate corresponding contents for search engine lookup tables. This verification-and-validation ability vastly reduces design time and eliminates iterations between system architects and network hardware engineers, allowing the teams to get highly differentiated products to market faster.

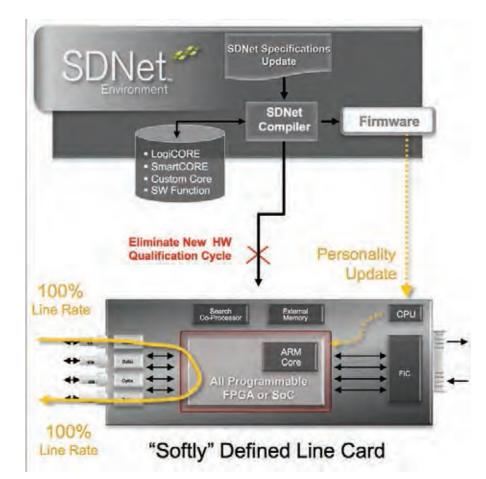

Gordon Brebner, distinguished engineer at Xilinx, said the compiler automatically generates custom firmware operations and their binary encodings for each individual component in the architecture. "This gives architects an intimate level of control over the processing," he said. SDNet has a utility that keeps a record of runs and stores details of the generated architecture and its firmware. When users rerun the compiler with an updated SDNet description as input, it determines whether the change can be accommodated with a firmware update only (without generation of new hardware), or whether a regeneration of the hardware (and firmware) is needed. In most cases, medium-scale updates, such as adding or subtracting a protocol the line card will handle, can be done through firmware updates only.

"The intimate connection between the firmware and the architecture, which are both generated by SDNet's compiler, means that users can perform hitless upgrades, whereby the firmware is changed and placed into service without disrupting the flow of packets," said Brebner. "In this way, companies can perform significant service upgrades without any interruption to the service. This revolutionary development is achieved through the unique nature of the SDNet technology and its coupling of high-level specifications with Xilinx All Programmable devices" (Figure 5).

"SDNet's ability to generate datapath processing functions that support hitless, in-service updates is unique," said Possley. "Carriers can update line card components with new features or capabilities using a software controller via standard SDNet APIs. They can run the updating software on an embedded soft processor or on an external processor." Of course, if they implemented the design on a Xilinx Zynq<sup>®</sup>-7000 All Programmable SoC, he added, they can run the software on the device's embedded ARM<sup>®</sup> processor.

"SDNet offers full hardware programmability under software control, which is why we call it 'softly' defined networking," Possley said.

For more information on the SDNet specification environment, including a video demonstration of SDNet in action, visit *www.xilinx.com/sdnet*. At the same site, you will find an indepth white paper entitled "Software Defined Specification Environment for Networking (SDNet)."

Figure 5 – After deployment, SDNet allows vendors to update protocols on line cards without interrupting service.

13

XCELLENCE IN WIRELESS

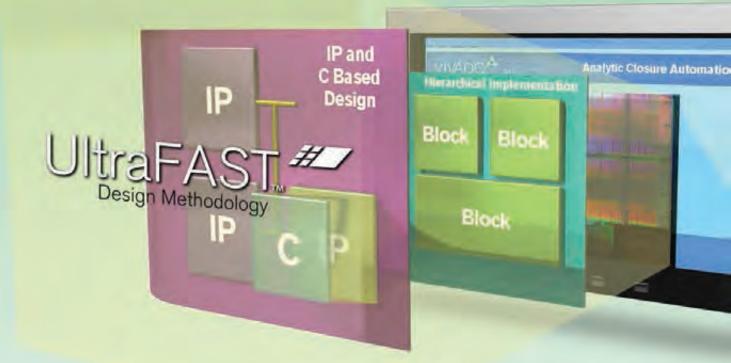

## Xilinx's 20-nm UltraScale Architecture Advances Wireless Radio Applications

Next-generation 5G systems will be complex to design. UltraScale devices have built-in functionality that will make the job easier.

by Michel Pecot

cond Quarter 2014

Wireless Systems Architect Xilinx, Inc. michel.pecot@xilinx.com pcoming 5G wireless communications systems will likely be required to support much wider bandwidths (200 MHz and larger) than the 4G systems used today, along with large antenna arrays, enabled by higher carrier frequencies, that will make it possible to build much smaller antenna elements. These so-called massive MIMO applications, together with more stringent latency requirements, will increase design complexity by an order of magnitude.

At the end of last year, Xilinx announced the 20-nanometer UltraScale<sup>™</sup> family and the first devices are now shipping [1,2,3]. This new technology brings many advantages over the previous 28-nm 7 Series generation, especially for wireless communications. Indeed, the combination of this new silicon and the tools of the Xilinx<sup>®</sup> Vivado<sup>®</sup> Design Suite [4, 5] is a perfect fit for high-performance signal-processing designs such as next-generation wireless radio applications.

Let's look at the benefits of the UltraScale devices for such designs, with a focus on architectural aspects specifically, the advantages of the enhancements brought to the DSP48 slices and Block RAMs for the implementation of some of the most common functionalities used in radio digital front-end (DFE) applications. The UltraScale family offers much denser routing and clocking resources compared with the 7 Series devices, enabling better device utilization, especially for high-speed designs. However, these features do not usually have a direct impact on design architectures, so we will not address them here.

#### OVERVIEW OF ENHANCEMENTS TO ULTRASCALE FABRIC

Moving to 20 nm not only enables the higher integration capabilities, improved fabric performance and lower power consumption that come with any geometry node migration, but the UltraScale 20-nm architecture also includes several new, greatly enhanced features that directly support DFE applications. This is especially true for the UltraScale Kintex<sup>®</sup> devices, which Xilinx has highly tuned to the needs of this type of design.

First, these devices contain up to 5,520 DSP48 slices. That's almost three times more than the maximum count of 1,920 available on 7 Series FPGAs (2,020 for the Zynq<sup>®</sup>-7000 All Programmable SoC). Higher levels of integration are therefore possible. For example, you can implement a complete 8Tx/8Rx DFE system with instantaneous bandwidth of 80 to 100 MHz in a single midrange UltraScale FPGA, while a two-chip solution is necessary on the 7 Series architecture, with each chip effectively supporting a 4x4 system. For a detailed functional description of such designs, read the Xilinx white paper WP445, "Enabling High-Speed Radio Designs with Xilinx All Programmable FPGAs and SoCs" [6].

## The serdes can support a throughput of 12.5 Gbps on slowest-speed-grade devices, enabling the maximum speed of JESD204B interfacing.

With the thermal constraints imposed by passively cooled remote radios, the integration of complex designs into a single device requires a significant power reduction to be able to dissipate the heat. The UltraScale family offers such a capability, with 10 to 15 percent less static power compared with 7 Series devices of the same size, and 20 to 25 percent less dynamic power for similar designs. Furthermore, Xilinx has also significantly lowered serdes power consumption in the UltraScale product line.

There is a performance advantage as well. The slowest-speed-grade UltraScale devices support designs with clock rates higher than 500 MHz, while midspeed grade is required for the 7 Series devices. However, even here, Block RAMs are still demanding from a timing perspective, and WRITE FIRST or NO CHANGE modes need to be selected to reach this kind of performance. You cannot use READ FIRST, since it is limited to around 470 MHz, while 530 MHz is achievable for the other two modes. NO\_CHANGE is your best choice whenever possible, since it also minimizes the power consumption.

Similarly, the serdes can support a throughput of up to 12.5 Gbps on the slowest UltraScale speed grade, hence enabling the maximum speed of JESD204B interfacing, which should be soon available on most DACs and ADCs. Similarly, the lowest speed grade can also support the two highest CPRI rates (rates 7 and 8, with respective throughputs of 9.8304 and 10.1376 Gbps) as well as 10GE interfaces, which are commonly used in DFE systems.

In addition, the UltraScale Kintex re-

source mix is better suited for radio applications, which results in a more optimal usage of the logic resources. The DSP-to-logic ratio, especially, is much more closely in line with what is typically required for DFE designs. More precisely, UltraScale Kintex devices have eight to 8.5 DSP48 slices per 1K lookup tables (LUTs), while this number is only around six on 7 Series devices.

Xilinx has also significantly increased the clocking and routing resources in the UltraScale architecture. This increase enables higher device utilization, especially for high-clock-rate designs. In effect, routing congestion is reduced, and designers can achieve better design packing and LUT utilization. In particular, LUT/SRL compression is more efficient. This is an interesting fabric feature that users can exploit to better pack their designs and consequently optimize resource utilization as well as dynamic power consumption, which can be reduced by a factor of up to 1.7 for the related logic. The principles of LUT/ SRL compression involve using the two outputs of the LUT6 to pack two different functions in a single LUT. In this way, you can pack two LUT5s, implementing a logic function or a memory, into a single LUT6, provided they share the same inputs or read/write address for a memory. Similarly, you can pack two SRL16s into a single LUT6.

This feature is quite useful for digital radio designs, which usually integrate many small memories sharing the same address—for instance, ROMs storing filter coefficients—and a lot of short delay lines (less than 16 cycles) to time-align different signal paths. Functions for data multiplexing, especially two-input multiplexers, can benefit from this feature too. LUT/SRL compression, however, must be used carefully when targeting high clock rates. First, you must use the two flip-flops connected to the O6/ O5 LUT outputs to avoid any timing issues. For the same reasons, it is recommended to apply this capability to related logic only, a strategy that also has the advantage of limiting routing congestion.

The clocking architecture and configurable logic block (CLB) also contribute to better device utilization in the UltraScale devices. Although the CLB is still based on that of the 7 Series architecture, there is now a single slice per CLB (instead of two), integrating eight, six-input LUTs and 16 flip-flops. The carry chain is consequently 8 bits long and a wider output multiplexer is available. In addition, Xilinx has also increased the control-set resources (that is, the clock, clock-enable and reset signals shared by the storage elements within a CLB).

However, it is essentially the improvements to the DSP48 slice and Block RAM that have the most impact on radio design architectures. Let's look at them more closely.

#### BENEFITS OF THE ULTRASCALE DSP48 SLICE ARCHITECTURE

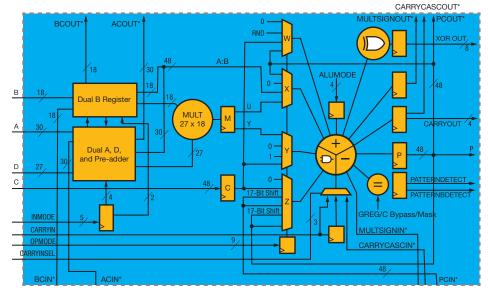

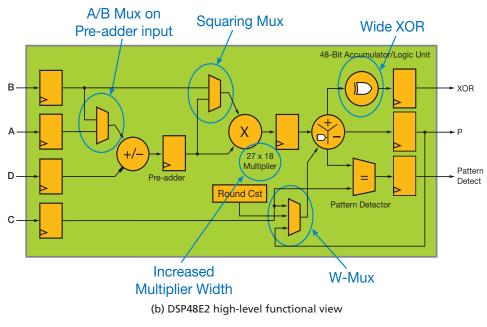

Figure 1 shows a view of the UltraScale DSP48 slice (DSP48E2). The top diagram (labeled "a") describes the detailed architecture, while the bottom part ("b") highlights the functional enhancements compared with the 7 Series slice (DSP48E1).

\* These signals are dedicated routing paths internal to the DSP48E2 column. They are not accessible via general-purpose routing resources.

(a) Detailed DSP48E2 architecture

Figure 1 – Architecture of the UltraScale DSP48 slice

The Xilinx user guide UG579 offers a comprehensive description of the DSP48E2 capabilities [7]. The major enhancements in the UltraScale architecture are:

- Xilinx has increased the multiplier width from 25x18 to 27x18, and the pre-adder width rises accordingly to 27 bits.

- You can select the pre-adder input to be either A or B, and some multiplexing logic has been integrated on

output, which allows feeding  $D \pm A$  or  $D \pm B$  on any of the multiplier inputs (27-bit or the 18-bit input).

- The pre-adder output can feed both multiplier inputs (with appropriate MSB truncation on the 18-bit input), hence allowing the computation of (D±A)<sup>2</sup> or (D±B)<sup>2</sup> for up to 18-bit data.

- A fourth operand is added to the arithmetic logic unit (ALU), through the extra W-mux multiplexer, which can take as input either C, P or a

constant value (defined at FPGA configuration). This makes it possible to perform a three-input operation when the multiplier is used, such as A\*B+C+P or A\*B+P+PCIN. It is worth noting that the W-mux output can only be added within the ALU (subtraction is not permitted).

• Xilinx has integrated additional logic to perform a wide XOR between the 96 bits of any two of the X, Y or Z multiplexer outputs. Four different modes are actually available, offering 1x 96-bit, 2x 48-bit, 4x 24-bit or 8x 12-bit XOR operation.

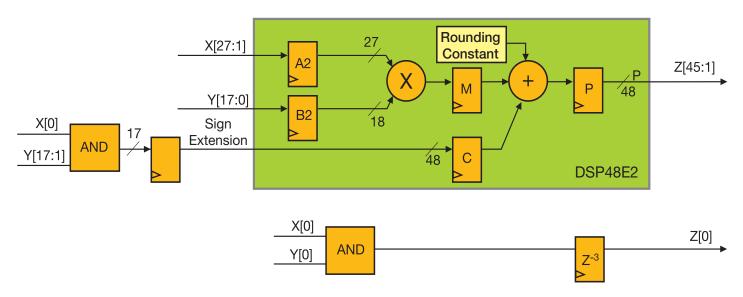

Increasing the multiplier size from 25x18 to 27x18 has minimal impact on the silicon area of the DSP48 slice, but significantly improves the support for floating-point arithmetic. First, it is worth pointing out that the DSP48E2 can in effect support up to 28x18-bit or 27x19-bit signed multiplication. This is achieved by using the C input to process the additional bit, as described in Figure 2, which shows the multiplication of a 28-bit operand, X, with an 18bit operand, Y.

The 45 most significant bits (MSBs) of the 46-bit output are computed as:

#### Z[45:1] = X[27:1]\*Y[17:0] + X[0]\*Y[17:1]

The 27 MSBs of X and 18 bits of Y are directly fed into the DSP48E2 multiplier inputs, while X[0]\*Y[17:1] is derived from an external 17-bit AND operator and sent to the C input after a single pipelining stage to match the DSP48E2 latency. The AND operator can actually be omitted by directly feeding Y[17:1] into a register with the reset pin controlled by X[0]. Similarly, an external 1-bit AND operator and a three-clockcycle delay for latency balancing are used to compute the LSB of Z, Z[0].

You can therefore implement a 28x18-bit multiplier with a single DSP48E2 slice and 18 LUT/flip-flop pairs. The same applies for a 27x19-bit multiplier, using 27 additional LUT/flip-flop pairs. In both cases, convergent

Figure 2 – A 28x18-bit signed multiplication with convergent rounding capability of the output

rounding of the result can still be supported through the W-mux.

A double-precision floating-point multiplication involves the integer product of the 53-bit unsigned mantissas of both operators. Although a 52-bit value (m) is stored in the double-precision floating-point representation, it describes the fractional part of the unsigned mantissa, and it is actually the normalized 1+m values, which need to be multiplied together; hence the additional bit required by the multiplication. Taking into account the fact that the MSBs of both 53-bit operands are equal to 1, and appropriately splitting the multiplication to optimally exploit the DSP48E2 26x17-bit unsigned multiplier and its improved capabilities (e.g., the true three-input 48-bit adder enabled by the W-mux), it can be shown that the 53x53-bit unsigned multiplication can be built with only six DSP48E2 slices and a minimal amount of external logic. It is out of the scope of this article to provide all the details of such an implementation, but a similar approach would require 10 DSP48E1 slices on the previous-generation 7 Series devices; hence there is a 40 percent gain brought by the UltraScale architecture.

The 27x18 multiplier of the DSP48E2 is also very useful for applications based on fused data paths. The concept of a fused multiply-add operator has been recently added to the IEEE floating-point standard [8]. Basically, it consists of building the floating-point operation A\*B+C, without explicitly rounding, normalizing and de-normalizing the data between the multiplier and the adder. These functions are indeed very costly when using traditional floating-point arithmetic and account for the greatest part of the latency. This concept may be generalized to build sum-of-products operators, which are common in linear algebra (matrix product. Cholesky decomposition). Consequently, such an approach is quite efficient for applications where cost or latency are critical, while still requiring the accuracy and dynamic range of the floating-point representation. This is the case in radio DFE applications for which the digital predistortion functionality usually requires some hardware-acceleration support to improve the update rate of the nonlinear filter coefficients. You can then build one or more floating-point MAC engines in the FPGA fabric to assist the coefficient-estimation algorithm running in software (e.g. on one of the ARM<sup>®</sup> Cortex<sup>TM</sup>-A9 cores of the Zynq SoC).

For such arithmetic structures, it has been shown that a slight increase of the mantissa width from 23 to 26 bits can provide even better accuracy compared with a true single-precision floating-point implementation, but with reduced latency and footprint. The UltraScale architecture is again well adapted for this purpose, since it takes only two DSP48 slices to build a single-precision fused multiplier, whereas three are required on 7 Series devices with additional fabric logic.

The pre-adder, integrated within the DSP48 slice in front of the multiplier, provides an efficient way to implement symmetric filters that are commonly used in DFE designs to realize the digital upconverter (DUC) and downconverter (DDC) functionality. For an N-tap symmetric filter, the output samples are computed as follows:

$$y(n) = \sum_{k=0}^{\left[\frac{N-1}{2}\right]} h(k) . (x(n-k) + x(n-N+1+k))$$

where x(n) represents the input signal and h(n) the filter impulse response, with h(n) = h(N-1-n).

Pairs of input samples are therefore fed into the pre-adder and the output is further multiplied with the appropriate filter coefficient. On the 7 Series architecture, the pre-adder must use the 30bit input (A) of the DSP48E1, together with the 25-bit input (D), and its output

## The addition of a fourth input operand to the ALU through the extra W-mux multiplexer brings the most benefit for radio applications.

is connected to the 25-bit input of the multiplier, while the B input is routed to the 18-bit multiplier input. Consequently, when building symmetric filters, the coefficients cannot be quantized on more than 18 bits, which limits the stopband attenuation to around 85 to 90 dB. This may be an issue for next-generation 5G radio systems, which are likely to operate in environments with a very high interference level, and may therefore need filters with greater attenuation.

The UltraScale architecture overcomes this problem because the pre-adder input can be selected as either A or B, and some multiplexing logic has been integrated on the output to allow feeding D $\pm$ A or D $\pm$ B to any of the multiplier inputs (27-bit or the 18-bit input). As a consequence, symmetric filters with up to 27-bit coefficients can be supported.

Another feature Xilinx has added to the DSP48E2 slice is the capability to connect the pre-adder output to both inputs of the multiplier (with appropriate MSB truncation on the 18-bit input). This makes it possible to perform operations such as  $(D\pm A)^2$  or  $(D\pm B)^2$  for up to 18-bit data, which can be used efficiently when evaluating sums of squared-error terms. Such operations are quite common in optimization problems, for example when implementing least-square solutions to derive the coefficients of the equalizer in a modem, or to time-align two signals.

It is indisputably the addition of a fourth input operand to the ALU, through the extra W-mux multiplexer, which brings the most benefit for radio applications. This operand can typically save 10 percent to 20 percent of the DSP48 requirements for such designs compared with the same implementation on a 7 Series device.

The W-mux output can only be added within the ALU (subtraction is not permitted), and can be set dynamically as the content of either the C or P register or as a constant value, defined at FPGA configuration (e.g. the constant to be added for convergent or symmetric rounding of the DSP48 output), or simply forced to 0. This allows performing a true three-input operation when the multiplier is used, such as A\*B+C+P, A\*B+C+PCIN, A\*B+P+PCIN, something that is not possible with the 7 Series architecture. Indeed, the multiplier stage generates the last two partial-product outputs, which are then added within the ALU to complete the operation (see Figure 1). Therefore, when enabled, the multiplier uses two inputs of the ALU, and a three-input operation cannot be performed on 7 Series devices.

Two of the ost significant examples that benefit from this additional ALU input are semi-parallel filters and complex multiply-accumulate (MAC) operators. Let's take a closer look at both of them.

#### **OF FILTERS AND MACS**

Linear filters are the most common processing units of any DFE application. When integrating such functionality on Xilinx FPGAs, it is recommended [6], as far as possible, to implement multichannel filters for which the composite sampling rate (defined as the product of the number of channels by the common signal-sampling frequency of each channel) is equal to the clock rate at which the design is running. In a so-called parallel architecture, each DSP48 slice supports a single filter coefficient per data channel, which greatly simplifies the control logic and hence minimizes the design resource utilization.

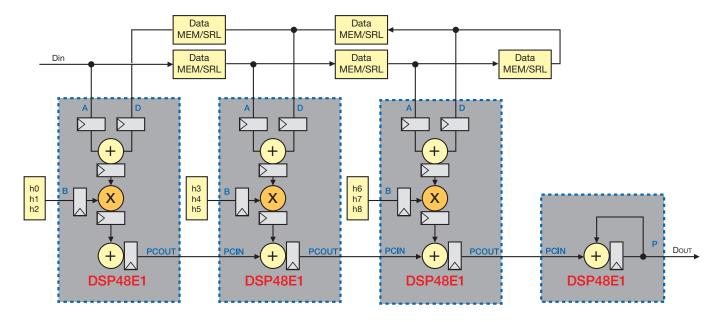

However, with higher clock-rate capabilities (for example, more than 500 MHz on lowest-speed-grade UltraScale devices), and for filters running at a relatively low sampling rate, it is often the case that the clock rate can be selected as a multiple of the composite sampling rate. It's desirable to increase the clock rate as much as possible to further reduce the design footprint, as well as the power consumption. In such situations, a semi-parallel architecture is built where each DSP48 processes K coefficients per channel, where K is the ratio between the clock rate and the composite sampling rate. The most efficient implementation then consists of splitting the filter into its K phases, each DSP48 processing a specific coefficient of these K phases.

At each clock cycle, the successive phases of the filter output are computed and need to be accumulated together to form an output sample (once every K cycle). Consequently, an additional accumulator is required at the filter output compared with a parallel implementation. This full-precision accumulator works on a large data width, equal to  $b_s+b_c+b_F$ , where  $b_s$  and  $b_c$  are respectively the bit widths of the data samples and coefficients, and  $b_F=Log_NN$  is the

filter bit growth, N being the total number of coefficients. Normal practice is therefore to implement the accumulator within a DSP48 slice to ensure support for the highest clock rate while minimizing footprint and power.

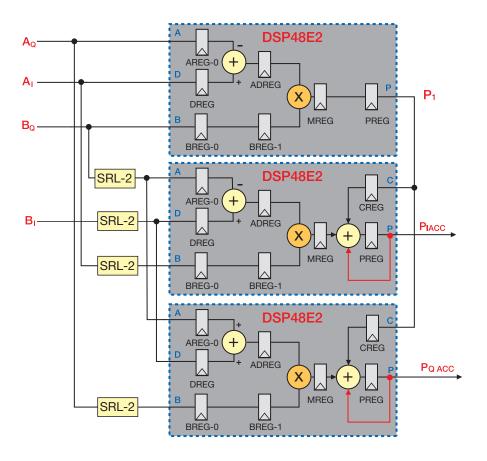

It should be noted that semi-parallel architectures can be derived for any type of filter: single-rate, integer or fractional-rate interpolation and decimation. Figure 3 shows a simplified block diagram for both 7 Series and UltraScale implementations. It clearly highlights the advantage of the UltraScale solution, since the phase accumulator is absorbed by the last DSP48 slice thanks to the W-mux capability.

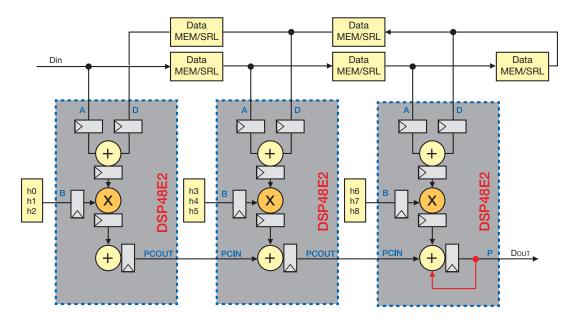

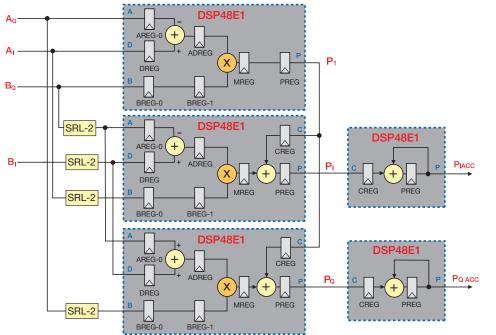

Let's now consider the implementation of a fully parallel complex MAC operator generating one output every clock cycle. It is well known that you can rewrite the equation of a complex product,  $P_I + j.P_Q = (A_I + j.A_Q).(B_I + j.B_Q)$ , so as to use only three real multiplications, according to:

•

$$P_I = P_1 + A_I \cdot (B_I - B_Q)$$

•

$$P_Q = P_1 + A_Q \cdot (B_1 + B_Q)$$

where

$$P_1 = B_Q \cdot (A_I - A_Q)$$

.

#### (a) 7 Series implementation

(b) UltraScale implementation

Figure 3 – Implementation of a semi-parallel filter on 7 Series and UltraScale architectures

(a) 7 Series implementation

(b) UltraScale implementation

Figure 4 – Implementation of a complex MAC on 7 Series and UltraScale architectures

Consequently, by exploiting the builtin pre-adder, you can implement a complex multiplier with three DSP48s onlyone to compute  $P_1$  and the other two to handle the  $P_{I}$  and  $P_{O}$  outputs. Depending on the latency requirements, which also dictate the speed performance, some logic needs to be added to balance the delavs between the different data paths. To get maximal speed support, the DSP48 must be fully pipelined, which results in an overall latency of six cycles for the operator. A two-cycle delay line is consequently added on each input to correctly align the real and imaginary data paths. Those are implemented with four SRL2 per input bit, which are in effect packed into two LUTs by taking advantage of the SRL compression capabilities.

The complex MAC is finally completed by adding an accumulator on each of the  $P_I$  and  $P_Q$  outputs. Again this accumulator works on large data widths and is therefore better integrated within a DSP48 slice. The corresponding implementations for 7 Series and UltraScale devices are shown in Figure 4, which once again demonstrates the benefit of the W-mux integration. The  $P_I$  and  $P_Q$  DSP48E2 slices absorb the accumulators, with 40 percent resource savings. It is worth mentioning that the latency is also reduced, which may be beneficial for some applications.

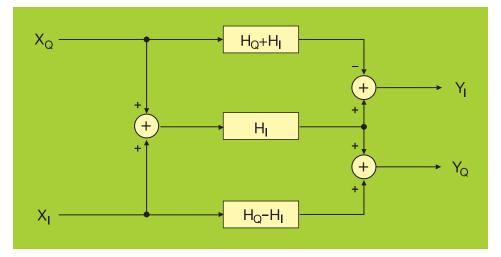

Using a similar construction, you can build a complex filter (one with complex data and coefficients) with three real filters, as depicted in Figure 5. The real and imaginary parts of the input signal are fed into two real filters, with coefficients derived respectively as the difference and sum of the imaginary and real parts of the filter coefficients. The third filter processes the sum of the input real and imaginary parts in parallel, using the real part of the coefficients.

The outputs of these three filters are finally combined to generate the real and imaginary components of the output, which can again benefit from the W-mux, when parallel filters need to be built, which is typically the case for the equalizers used in DFE applications.

Figure 5 – Implementation architecture of a complex filter

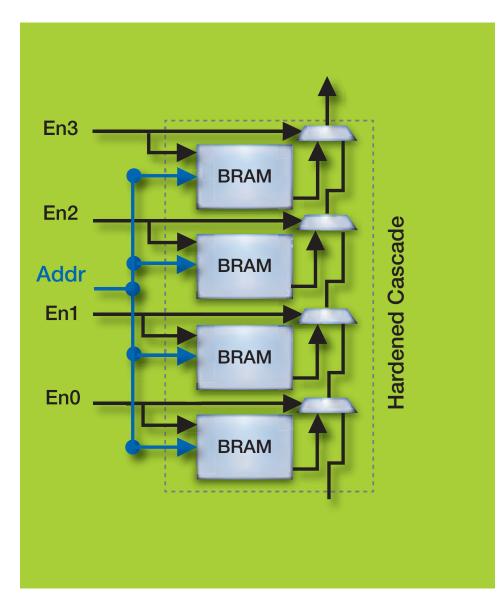

Figure 6 - BRAM cascade on UltraScale devices

#### BENEFITS OF THE ULTRASCALE MEMORY ARCHITECTURE

The Block RAMs integrated in Ultra-Scale devices are essentially the same as in the 7 Series, but the new architecture introduces a hardware data-cascading scheme, together with a dynamic power-gating capability. Figure 6 illustrates this cascade, showing the data multiplexers embedded between every lower and upper adjacent Block RAM in a column. Larger memories can therefore be built in a bottom-up fashion without additional use of logic resources.

The cascade covers each entire column across the device, but its usage is better limited to a single clock region (that is, 12 successive BRAMs) to avoid clock skew and to maximize timing performance. Full flexibility is also available to support different implementations of the cascade feature. In effect, you can apply the multiplexer either to the Block RAM data input or to the output after or before the optional register.

The cascade opens up the possibility of building large memories requiring more than one BRAM, while simultaneously supporting minimal footprint, highest clock rate and minimal power, which is not feasible with 7 Series devices. For example, a 16K memory storing 16-bit data is better implemented with eight BRAMs (36K) configured as 16Kx2-bit on a 7 Series device to avoid external data multiplexing, which would add logic resources and latency, and could impact timing and routing congestion. This is unfortunately the less-efficient approach from a dynamic-power perspective, since the eight Block RAMs are enabled during any read or write operation. The optimal solution consists of using a 2Kx16-bit configuration, since only a single BRAM is then enabled, which divides the dynamic power by a factor 8. This is precisely what the cascade feature enables on the UltraScale devices, together with the dynamic power-gating capability.

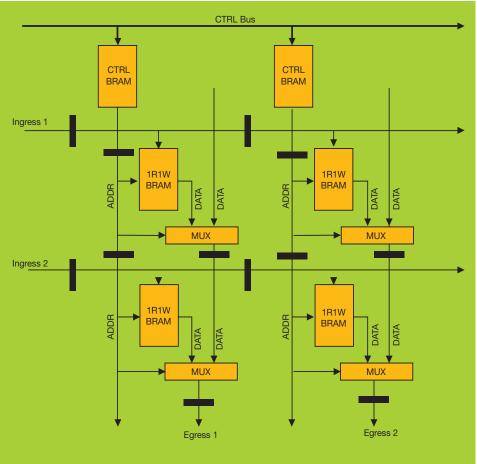

Another direct application of the Block RAM cascade is related to the implementation of I/Q data-switching functionality, commonly integrated with the baseband CPRI interfacing of DFE systems. Figure 7 shows the high-level switching architecture, which essentially consists of an NxM memory array. The successive data on the N ingress streams are written into the appropriate Block RAM in a line according to their output destination, and the M egress streams are read out from the appropriate Block RAM in a column. Consequently, each column can effectively be implemented with the BRAM cascade.

For more information on the 20-nm UltraScale family, visit *http://www.xilinx.com/products/silicon-devices/fpga/index.htm*.

#### References

1. Xilinx backgrounder, "Introducing UltraScale Architecture: Industry's First ASIC-Class All Programmable Architecture," July 2013

- 2. Xilinx white paper WP435, "Xilinx UltraScale: The Next Generation Architecture for Your Next Generation Architecture," July 8, 2013

- Xilinx datasheet DS890, "UltraScale Architecture and Product Overview," Feb. 6, 2014

- 4. Xilinx backgrounder, "9 Reasons why the Vivado Design Suite Accelerates Design Productivity," July 2013

- Xilinx user guide UG949, "Design Methodology Guide for the Vivado Design Suite," July 5, 2013

- 6. Xilinx white paper WP445, "Enabling High-Speed Radio Designs with Xilinx All Programmable FPGAs and SoCs," Jan. 20, 2014

- Xilinx user guide UG579, "UltraScale Architecture—DSP Slice, Advance Specification User Guide," Dec. 10, 2013

- IEEE Computer Society, "IEEE Standard for Floating Point Arithmetic, IEEE Std 754-2008," Aug. 29, 2008

Figure 7 - Data-switching high-level architecture

difference by design

www.trenz-electronic.de

XCELLENCE IN INDUSTRIAL

## Angle Measurement Made Easy with Xilinx FPGAs and a Resolver-to-Digital Converter

When properly paired with an FPGA, angle transducers can help engineers create ever-more-remarkable machinery. **by N. N. Murty** Scientist "F"

**S. B. Gayen** Scientist "F"

Manish Nalamwar Scientist "D" nalamwar.manishkumar@rcilab.in

K. Jhansi Lakshmi, Technical Officer "C" Radar Seeker Laboratory Research Centre IMARAT Defense Research Development Organization Hyderabad, India ver since humans invented the wheel, we have wanted to know, with varying degrees of accuracy, how to make wheels turn more efficiently. Over the course of the last few centuries, scientists and engineers have studied and devised numerous ways to accomplish this goal, as the basic

principles of the wheel-and-axle system have been applied to virtually every mechanical system, from cars to stereo knobs to cogs in all forms of machinery, to the humble wheelbarrow [1].

Over these many eras, it turns out the most essential element in making a wheel turn efficiently is not the wheel itself (why reinvent it?) but the shaft angle of the wheel. And the most effective way to measure and optimize a shaft angle today is through the use of angle transducers. There are many types of angle transducers that help optimize wheel efficiency through axle monitoring and refinements, but by applying FPGAs to the task you can achieve remarkable results and improve axle/wheel efficiencies in a broad number of applications.

Before we get into the details of how engineers are doing this optimally with Xilinx<sup>®</sup> FPGAs, let's briefly review some basic principles of angle transducers. Today there are two widely used varieties: encoders and resolvers.

#### **TYPES OF ENCODERS AND RESOLVERS**

Encoders fall into two basic categories: incremental and absolute. Incremental encoders monitor two positions on an axle and create an A or B pulse each time the axle passes those positions. A separate external electric counter then interprets those pulses for speed and rotational direction. Incremental counters are useful in a number of applications, but they do have some disadvantages. For example, when the axle is powered off, an incremental encoder must first calibrate itself by returning to a desig-

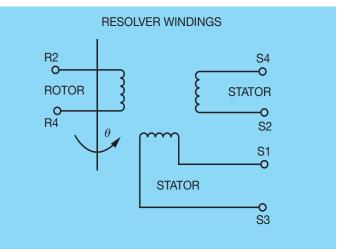

Figure 1 - Excitation to the rotor of a resolver

nated calibration point before beginning operation. Incremental counters are also susceptible to electrical interference, which can result in inaccuracies in pulses they send to the system and thus in rotation counts. Moreover, many incremental encoders are photoelectric devices, which precludes their use in radiation-hazardous areas, if that is a concern for your targeted application.

Absolute encoders are sensor systems that monitor the rotation count and direction of an axle. In an absolute-encoder-based system, users typically attach a wheel to an axle that has an electrical contact or photoelectric reference. When the axle is in operation, the absolute-encoder-based system records the rotation and direction of the operation and generates a parallel digital output that is easily translated into code, most commonly binary or Gray code. Absolute encoders are useful in that they need to be calibrated only once—typically in the factory—and not before every use. Moreover, they are typically more reliable than other encoders. That said, absolute encoders are typically expensive, and they are not great with parallel data transmission, especially if the encoder is located far away from the electronic system measuring its readings.

A resolver, for its part, is a rotary transformer—an ana-

log device whose output voltage is uniquely related to the input shaft angle it is monitoring. It is an absolute-position transducer with 0° to 360° of rotation that connects directly to the axle and reports speed and positioning. Resolvers have a number of advantages over encoders. They are robust devices that can withstand harsh environments marked by dust, oil, temperature extremes, shock and radiation. Being a transformer, a resolver provides signal isolation and a natural common-mode rejection of electrical interference. In addition to these features, resolvers require only four wires for the angular data transmission, which suits them for everything from heavy manufacturing to miniature systems to those used in the aerospace industry.

A further refinement is the brushless resolver, which does not require slip-ring connections to the rotor. This type of resolver is therefore even more reliable and has a longer life cycle.

Resolvers use two methods to obtain output voltages related to the shaft angle. In the first method, the rotor winding, as shown in Figure 1, is excited by an alternating signal and the output is taken from the two stator windings. As the stator windings are mechanically positioned at right angles, the output signal amplitude is related by the trigonometric sine and cosine of the shaft angle. Both the

Figure 2 - Resolver-to-digital converter (RDC) block diagram

sine and cosine signals have the same phase as the original excitation signal; only their amplitudes are modulated by sine and cosine as the shaft rotates.

In the second method, a stator winding is excited with the alternating signals, which are in phase quadrature to each other. Then a voltage induces in the rotor winding. The winding's amplitude and frequency are fixed, but its phase shift varies with the shaft angle.

The resolver can be positioned where the angle needs to be measured [2]. The electronics, generally a resolver-to-digital converter (RDC), can be positioned where the digital output needs to be measured. Analog output from the resolver, which contains the angular position information of the shaft, is then transformed in digital form using the RDC.

FUNCTIONALITY OF THE TYPICAL RDC

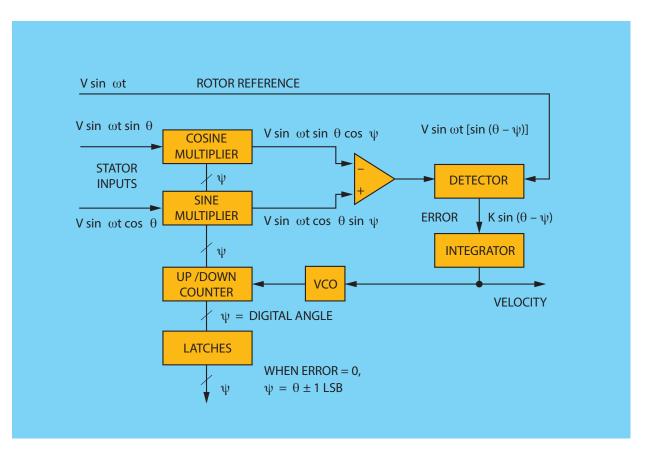

In general, the two outputs of a resolver are applied to the sine and cosine multiplier of the RDC [3]. These multipliers incorporate sine and cosine lookup tables and function as multiplying digital-to-analog converters. Figure 2 shows their functionality.

Let us assume, in the beginning, that the current state of the up/down counter is a digital number representing a trial angle,  $\psi$ . The converter seeks to adjust the digital angle,  $\psi$ , continuously to become equal to and track  $\theta$ , the analog angle being measured.

The stator output voltage of the resolver is:

| $V1 = V \sin\omega t \sin\theta$ | Eq. 1 |

|----------------------------------|-------|

| $V2 = V \sin\omega t \cos\theta$ | Eq. 2 |

where  $\theta$  is the angle of the resolver's rotor. The digital angle  $\psi$  is applied to the cosine multiplier and its cosine is multiplied by V1 to produce the term:

V sin

$$\omega$$

t sin $\theta$  cos $\psi$ . Eq. 3

The digital angle  $\psi$  is also applied to the sine multiplier and multiplied by V2 to produce the term:

V sin $\omega$ t cos $\theta$  sin $\psi$ . Eq. 4

These two signals are subtracted from each other by the error amplifier to yield an ac error signal of the form:

| $(V \sin\omega t \sin\theta \cos\psi - V \sin\omega t \cos\theta \sin\psi)$ | Eq. 5 |

|-----------------------------------------------------------------------------|-------|

| $V\sin\omega t (\sin\theta\cos\psi - \cos\theta\sin\psi)$                   | Eq. 6 |

|                                                                             |       |

From trigonometric identity, this reduces to:

$$V \sin\omega t \left[ \sin \left( \theta - \psi \right) \right]$$

Eq. 7

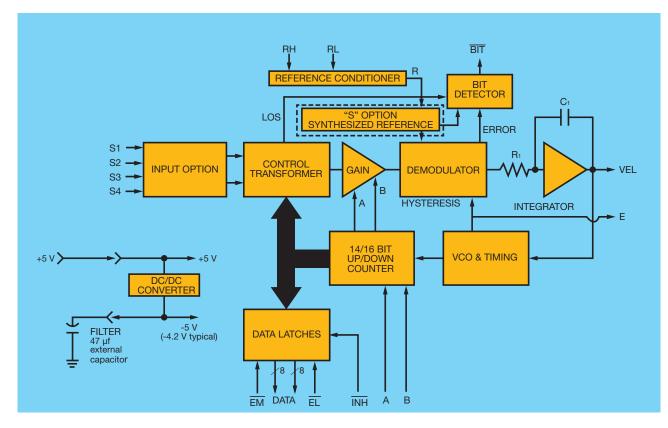

Figure 3 – SD-14620 block diagram (one channel)

Figure 4 – Block diagram of the OSC-15802 reference oscillator

The detector synchronously demodulates this ac error signal, using the resolver's rotor voltage as a reference. This results in a dc error signal proportional to  $\sin(\theta - \psi)$ .

The dc error signal feeds an integrator, the output of which drives a voltage-controlled oscillator. The VCO, in turn, causes the up/down counter to count in the proper direction to cause:

$\sin(\theta - \psi) \rightarrow 0.$  Eq. 8

When this result is achieved,

$$\theta - \psi \rightarrow 0,$$

Eq. 9

and therefore

f

$$\theta = \psi$$

Eq. 10

in one count. Hence, the counter's digital output,  $\psi$ , represents the angle  $\theta$ . The latches make it possible to transfer this data externally without interrupting the loop's tracking.

This circuit is equivalent to a Type 2 servo loop, as it has in effect two integrators. One is the counter, which accumulates pulses; the other is the integrator at the output of the detector. In a Type 2 servo loop with a constant-rotational-velocity input, the output digital word continuously follows, or tracks, the input, without needing externally derived conversion.

#### **TYPICAL EXAMPLE OF AN RDC: THE SD-14621**

The SD-14621 is a small, low-cost, RDC from Data Device Corp. (DDC). It has two channels with programmable resolution control. Resolution programming allows selection of 10-, 12-, 14- or 16-bit modes [4]. This feature allows low resolution for fast tracking or higher resolution for higher accuracy. Thanks to its size, cost, accuracy and versatility, this converter is suitable for high-performance military, commercial and position-control systems.

28 Xcell Journal

A single +5 V is required for device operation. The converter has velocity outputs (VEL A, VEL B) of a voltage range of  $\pm 4$  V with respect to analog ground, which can be used to replace a tachometer. Two built-in test outputs are provided for two channels (/BIT A and /BIT B) to indicate loss of signal (LOS).

This converter has three main sections: an input front end, an error processor and a digital interface. The front end differs for synchro, resolver and direct inputs. An electronic Scott-T is used for synchro inputs, a resolver conditioner for resolver inputs and a sine-and-cosine voltage follower for direct inputs. These amplifiers feed the high-accuracy control transformer (CT). The other input of the CT is a 16bit digital angle  $\psi$  and the output is an analog error angle, or a difference angle, between the two inputs. The CT performs the ratiometric trigonometric computation of SIN $\theta$ COS $\psi$  - COS $\theta$  SIN $\psi$  = Sin( $\theta$ - $\psi$ ) using amplifiers, switches, logic and capacitors in precision ratios.

Compared with a conventional precision resistor, these capacitors are used in precision ratios to get enhanced accuracy. Further, these capacitors (which are used with an op amp as a computing element) sample at high rates to eliminate drift and op-amp offsets.

The DC error processing is integrated, yielding a velocity voltage that drives a voltage-controlled oscillator. This VCO is an incremental integrator when it is combined with the velocity integrator: a Type 2 servo feedback loop.

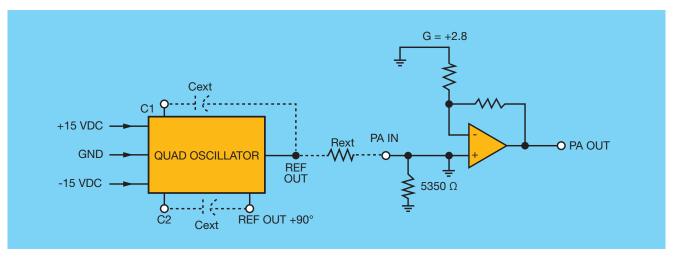

#### **REFERENCE OSCILLATOR**

The power oscillator in our design, also from DDC, is the OSC-15802. This device is suitable for RDC, synchro, LVDT, RVDT and inductosyn applications [5]. The frequency and amplitude outputs are programmable with capacitors and resistors, respectively. The output frequency range is 400 Hz to

## The I/O voltage of the FPGA is 3.3 V, while the RDC's voltage is 5 V. We used voltage transceivers to achieve voltage compatibility between the two devices.

10 kHz, with an output voltage of 7 Vrms. Figure 4 shows a block diagram of the device.

The oscillator output, which is given to the resolver and the RDC, works as a reference signal.

#### **VIRTEX-5 FX30T FPGA AND RDC INTERFACE**

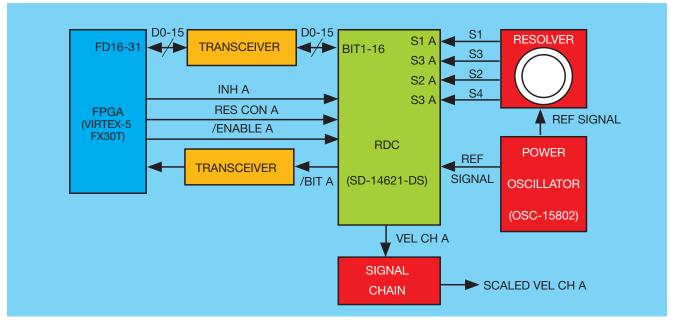

For our design, we used a Xilinx Virtex<sup>®</sup>-5 FX30T FPGA [6]. The I/O voltage of the FPGA is 3.3 V, while the RDC's voltage is 5 V. We used voltage transceivers to achieve voltage compatibility between the two devices. Internal connections with the FPGA are established through the GPIO IP core provided by Xilinx, as seen in Figure 5.

For simplicity's sake, Figure 5 shows just one channel with the single resolver interface. <u>You will find the pin details of the RDC and corresponding pin locking with the FPGA in the Xilinx Board Description (XBD) file that accompanies this article.</u> The details are listed in Section 1 of that document.

#### **DETAILS OF THE DEVICE DRIVER**

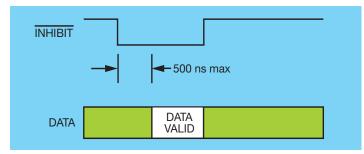

In this case, we used an external input clock of 20 MHz for the FPGA. This FPGA has a hard PowerPC<sup>®</sup> 440 core that is running at a 200-MHz frequency. The timing diagram of the RDC is shown in Figure 6 and Figure 7.

In accordance with the timing diagram of the RDC, we developed, tested and confirmed correct functionality with the actual hardware [4]. The actual code of the device driver is included in the separate XBD file. As per the timing diagram, we generated required delays using for loops. When processing is running at 200 MHz, each count corresponds to a delay of 5 nanoseconds.

The device driver has three sections of code: RDC initialization; generation of a control signal and reading from channel A of the RDC; and generation of a control signal and reading from channel B. RDC initialization is the point at which the direction of the signal and default values are

Figure 5 - RDC interface with the Virtex-5 FPGA (single channel)

set. For example, with the following statement, the direction is set as "out" from the FPGA to the RDC.

#### XGpio\_WriteReg(XPAR\_RESOLUTION\_CNTRL\_CH\_A\_ BASEADDR,XGPIO\_TRI\_OFFSET,0x000);

With the next statement, the 16-bit resolution is set by writing "0x3" (that is, pulling high):

#### XGpio\_WriteReg(XPAR\_RESOLUTION\_CNTRL\_CH\_A\_ BASEADDR,XGPIO\_DATA\_OFFSET,0x03);

Figure 8 shows a snapshot of the coding. Note: for simplification, we have included code for only one channel.

As we have seen, angle transducers help engineers create a better wheel and thus a plethora of more efficient machinery. Resolvers are an especially useful type of angle transducer, and when properly paired and controlled with an FPGA, can help engineers create even more remarkable machinery.

#### References

- 1. "Synchro/Resolver Conversion Handbook," Data Device Corp.

- 2. John Gasking, "Resolver-to-Digital Conversion: A Simple and Cost-Effective Alternative to Optical Shaft Encoders," AN-263, Analog Devices

- 3. Walt Kester, "Resolver to Digital Converter," MT-030, Analog Devices

- 4. SD-14620 Series Data Sheet, Data Device Corp.

- 5. OSC-15802 Data Sheet, Data Device Corp.

- 6. "Virtex-5 Family Overview," Xilinx

Figure 7 – ENABLE timing

```

for(i=0;i<=5;i++);

XGpio_WriteReg(XPAR_INHIBIT_CH_A_BASEAD-

DR,XGPIO_DATA_OFFSET,0x00);

for(i=0;i<=2;i++);

XGpio_WriteReg(XPAR_ENABLE_LSB_CH_A_BIT_

BASEADDR,XGPIO_DATA_OFFSET,0x00);</pre>

```

```

for(i=0;i<=2;i++);

```

```

lsb_val=XGpio_ReadReg(XPAR_RDC_DATA_15_

TO_0_PINS_BASEADDR,XGPIO_DATA_OFFSET);

```

```

XGpio_WriteReg(XPAR_INHIBIT_CH_A_BASEAD-

DR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=5;i++);

XGpio_WriteReg(XPAR_ENABLE_LSB_CH_A_BIT_

BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=25;i++);</pre>

```

```

XGpio_WriteReg(XPAR_INHIBIT_CH_A_BASEAD-

DR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=5;i++);

XGpio_WriteReg(XPAR_ENABLE_MSB_CH_A_BIT_

BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=5;i++);</pre>

```

```

XGpio_WriteReg(XPAR_INHIBIT_CH_A_BASEAD-

DR,XGPIO_DATA_OFFSET,0x00);

for(i=0;i<=2;i++);

XGpio_WriteReg(XPAR_ENABLE_MSB_CH_A_BIT_

BASEADDR,XGPIO_DATA_OFFSET,0x00);

for(i=0;i<=2;i++);

msb_val=XGpio_ReadReg(XPAR_RDC_DATA_15_

TO 0 PINS BASEADDR,XGPIO_DATA_OFFSET);

```

lsb\_val=lsb\_val & 0x00ff;

msb\_val=msb\_val & 0xff00;

rdccount\_cha = msb\_val | lsb\_val;

XGpio\_WriteReg(XPAR\_INHIBIT\_CH\_A\_BA-SEADDR,XGPIO\_DATA\_OFFSET,0X01); for(i=0;i<=5;i++);</pre>

```

XGpio_WriteReg(XPAR_ENABLE_MSB_CH_A_

BIT_BASEADDR,XGPIO_DATA_OFFSET,0x01);

for(i=0;i<=20;i++);</pre>

```

Figure 8 - A snapshot of RDC device driver code

## TRACE32®

Debugging Xilinx's Zynq<sup>™</sup> -7000 family with ARM CoreSight

- RTOS support, including Linux kernel and process debugging

- ► SMP/AMP multicore Cortex™-A9 MPCore™s debugging

- Up to 4 GByte realtime trace including PTM/ITM

- ► Profiling, performance and statistical analysis of Zynq's multicore Cortex<sup>™</sup> -A9 MPCore<sup>™</sup>

LAUTERBACH DEVELOPMENT TOOLS

### Is your marketing message reaching the right people?

XCELLENCE IN INDUSTRIAL

## Motor Drives Migrate to Zynq SoC with Help from MATLAB

Second Ouarter 2014

**by Tom Hill** Senior Manager, DSP Solutions Xilinx, Inc. *tom.hill@xilinx.com*

Industrial designers can use rapid prototyping and model-based design to move their motor control algorithms to the Zynq SoC environment.

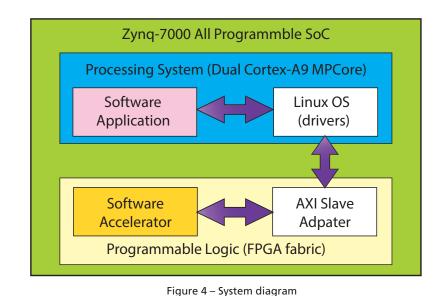

ince the 1990s, developers of motor drives have been using a multichip architecture to implement their motor control and processing requirements. In this architecture, a discrete digital signal-processing (DSP) chip executes motor control algorithms, an FPGA implements high-speed I/O and networking protocols, and a discrete processor handles executive control. With the advent of the Xilinx<sup>®</sup> Zynq<sup>®</sup>-7000 All Programmable SoC, however, designers have the means to consolidate these functions into a single device while integrating additional processing tasks. The reduction in parts count and complexity makes it possible to lower system cost while improving performance and reliability.

But how can drive developers evolve their established design practices to leverage the Zynq SoC?

Industrial designers have long embraced model-based design for the development of custom motor algorithms on DSP chips through the use of simulation and C-code generation. Now, a new workflow from MathWorks—developed in conjunction with Xilinx—extends model-based design to the processing system and programmable logic available with the Zynq-7000 All Programmable SoC.

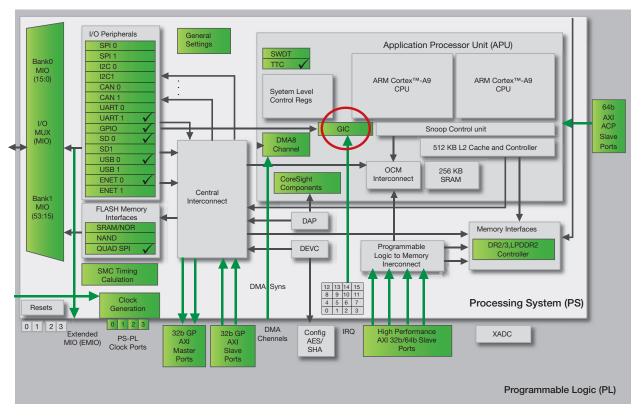

#### **ZYNQ SOCS FOR MOTOR CONTROL**

Today's advanced motor control systems are a combination of control algorithms and industrial networks, including EtherCAT, Profinet, Powerlink and Sercos III, that draw processing bandwidth from the computing resources. Moreover, other requirements are converging into the control system including motion-control layers, PLC layers, diagnostic layers and user interfaces for commission and maintenance or remote monitoring. These requirements translate into logical and physical partitions with elements that fit naturally into the processing systems while other elements best fit into the hardware-assisted offloading and acceleration.

The hardware platform you select should provide a robust and scalable system. Xilinx's Zynq SoCs fulfill these requirements by supplying a high-performance processing system to address the networking, motion, soft-PLC, diagnostic and remote-maintenance functions combined with programmable logic to accelerate performance-critical functions in hardware. On the processing side, the Zynq SoC

Figure 1 – MathWorks' workflow targeting the Zynq SoC, using C and HDL code generation

combines a dual-core ARM<sup>®</sup> Cortex<sup>TM</sup>-A9 processing system with a NEON coprocessor and floating-point extensions to accelerate software execution. On the programmable logic side, the device has up to 444,000 logic cells and 2,200 DSP48 slices that supply massive processing bandwidth. Five high-throughput AMBA<sup>®</sup>-4 AXI high-speed interconnects tightly couple the programmable logic to the processing system with the equivalent of more than 3,000 pins of effective bandwidth.

Table 1 lists the processing performance that Zynq SoC devices can achieve.

#### PLANT AND MOTOR MODELING USING SIMULINK AND THE CONTROL SYSTEMS TOOLBOX

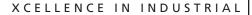

Modern control algorithms have system times and system variables that span several orders of magnitude, making hardware/software partitioning a daunting, time-consuming and iterative task. Figure 2 depicts a typical electrical drive. The power source is normally 50 to 60 Hz and is rectified to achieve a continuous voltage (DC). This DC voltage is then converted into a variable frequency that controls the power stage that feeds the motor terminals. The controller also must read the motor's basic variables including current and voltages. It likewise must read or establish the shaft position including its speed and handling commands originating from the communication network or supervising controller.

Simulink<sup>®</sup> provides a block-diagram environment for multidomain system simulation and model-based design that is well suited to simulating systems that include control algorithms and plant models. MathWorks products such as the Control Systems Toolbox provide a variety of "apps" based on widely used methods of systematically analyzing, designing and tuning control systems modeled in Simulink. Performing system modeling in Simulink can accelerate development of motor control systems while reducing risk in the following ways:

- **Reduces risk of damage** Simulation allows thorough examination of new control system algorithms before they are tested on production hardware, where there are risks of damaging drive electronics, motors and other system components.

- Accelerates system integration – Support staff must integrate new control system algorithms into the

| Elements                 | Performance (up to) |  |  |

|--------------------------|---------------------|--|--|

| Processors (each)        | 1 GHz               |  |  |

| Processors (aggregate)   | 5,000 DMIPs         |  |  |

| DSP (each)               | 741 MHz             |  |  |

| DSP (aggregate)          | 2,662 GMACs         |  |  |

| Transceivers (each)      | 12.5 Gbps           |  |  |

| Transceivers (aggregate) | 200 Gbps            |  |  |

| Software acceleration    | 10x                 |  |  |

Table 1 – Processing performance of the Zynq SoC

production system, meaning that deploying new controllers can consume their limited time and can make the deployment a protracted process.

• Reduces dependency on equipment availability – The production environment itself may not be available, such as in cases where custom drive electronics or electric motors are under development or are not located where control system designers can access them.

Given these factors, simulation provides an excellent alternative to testing on production hardware. Simulation environments such as Simulink provide a framework for creating plant models from preexisting libraries of building blocks of electromechanical components for the evaluation of new control system architectures against plant models.

Risk to the schedule is further reduced by linking the system model to a rapid-prototyping environment as well as the final production system. The rapid-prototyping flow enables algorithm developers to prototype without having to depend on hardware designers. Instead they use a platform-specific support package in a highly automated process that deploys the hardware and software components of the system to a design template that can be compiled to a specific hardware development platform. The hardware and software design teams can reuse these same hardware and software components in the final production systems without modification to accelerate development and reduce errors.

#### RAPID PROTOTYPING USING THE AVNET INTELLIGENT DRIVES KIT

Designers can pair the Avnet Zynq-7000 AP SoC / Analog Devices Intelligent Drives Kit with Simulink and the Zynq SoC workflow for a complete rapid-prototyping system for motor control applications. This kit combines the Zynq SoC with the latest generation of Analog Devices' high-precision data converters and digital isolation. The kit enables high-performance motor control and dual Gigabit Ethernet industrial networking connectivity (*http://www.xilinx.com/products/ boards-and-kits/1-490M1P.htm*).

It comes with an Avnet ZedBoard 7020 baseboard; Analog Devices' AD-FMCMOTCON1-EBZ module, which is capable of driving brushless DC and stepper motors with a 24-volt external power supply (included with the kit); and a 24-V BLDC motor rated for 4,000 RPM and equipped with Hall-effect sensors and a 1,250-CPR indexed encoder. Also included are a Zynq SoC reference design of field-oriented control and Analog Devices' Ubuntu Linux framework including drivers, application software and source code.

#### EXAMPLE: TRAPEZOIDAL MOTOR CONTROL

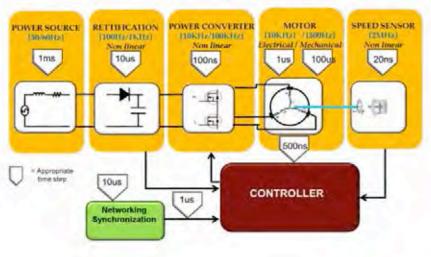

Let's apply this workflow to the trapezoidal motor control system in Figure 1 using simulation in Simulink to evaluate a controller with a simulated plant, then prototype the controller using the Intelligent Drives Kit. As a final step, we will validate the Simulink model using results from hardware testing.

In this example, we will use the kit to drive an inertial load in the form of an aluminum disc, with a basic trapezoidal controller. The controller's main components are as follows:

- Hall-effect sensor detects the motor position

- Velocity estimator computes rotor velocity based on the sensor signal

- Six-step commutator computes the phase voltages and inverter enable signals based on rotor position and velocity

- Pulse-width modulation (PWM) drives the controller outputs out through the drive circuitry

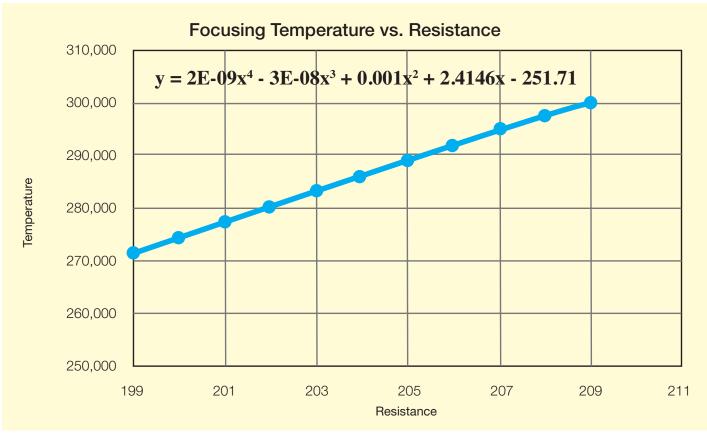

We start by using a behavioral, control-loop model of the system suited to control-loop analysis. First we will evaluate the model in simulation by subjecting it to a pulse test, commanding a rotational rate of 150 radians per second for 2 seconds and then returning to a stop. Through tuning of the control loop's proportional-integral (PI) controller gains, we can achieve a settling time of 1.2 seconds with negligible overshoot (control-loop simulation results appear as the purple-shaded signal in Figure 3; details on this example are available at *mathworks.com/zidk*).

Electric Drive Control – Major Time Contstraints Where the performances are needed in the control portion

Figure 2 - Major time constraints of electrical drive controllers

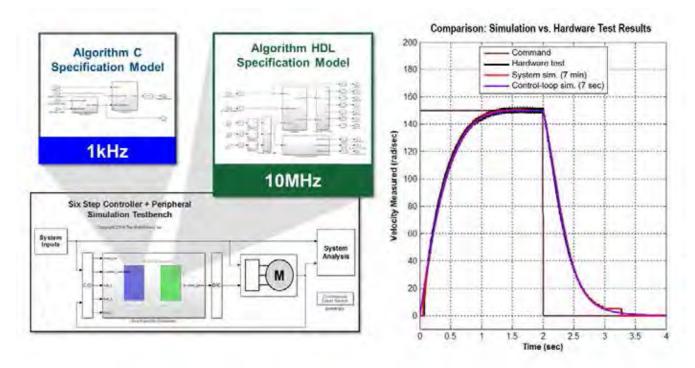

Figure 3 - Hardware and software simulation models used to validate against hardware results

Six Step Commutator And Peripherals

HDL Specification

#### Algorithm HDL Specification Model

Generates HDL code for the algorithm that you can integrate into your design template

|                               | ENTITY Bitstream IS |      |     |                                |

|-------------------------------|---------------------|------|-----|--------------------------------|

| and particular and the second | PORT ( CLR_IN       | 1 3  | IN  | sta logio;                     |

| 응 신 . ㅋㅋㅋㅋ                    | repet               | 1    | IN  | std logic:                     |

|                               | clk_enable          | 5 2  | IN  | std_logic;                     |

| 9-11-1-1                      | hall_s              | ± 0  | IN. | and logic:                     |

| interest in the second        | hall_b              | ± 9  | IN  | std_logic:                     |

|                               | hall c              | 2 6  | IN. | std logic;                     |

|                               | aki_motor_co        | t (  | IN  | std logic:                     |

|                               | axi voltage level   | 1. 0 | IN  | std logic vector(17 DOWNTO 0); |

|                               | ce out              | 4. 1 | TUO | std logic;                     |

Figure 4 – C and HDL code generated from partitioned Simulink model

0

CO-to

With the control-loop gains set, we now can test on a more accurate system model for the controller. In contrast to the control-loop model, the system model incorporates more detailed models of the drive electronics and, more significantly, it includes detailed models that specify the implementation of the controller and peripherals, including timing-accurate models for PWM and Hall-effect sensor processing.

We have partitioned the controller for the Zynq SoC, with the velocity controller and velocity estimator running on an ARM core at 1 kHz and the commutator, Hall sensor and PWM running on the Zynq SoC's programmable logic.