## **Xilinx ML Suite Overview**

Yao Fu System Architect – Data Center Acceleration

## Xilinx Accelerated Computing Workloads

| Machine Learning Inference Image classification and object detection | 10x  | <b>E</b> XILINX                           |

|----------------------------------------------------------------------|------|-------------------------------------------|

| Video Streaming Frame rate for HEVC & VP9 encoding                   | 10x  | NEST GENERALION VIDEO COMPRESSION         |

| Genomics 20 min vs. 33 hours for whole genome analysis               | 100x | edico genome                              |

| Big Data Analytics 40 min vs. 60 hours for logfile query             | 90x  | ACTIONABLE INTELLIGENCE FROM COMPLEX DATA |

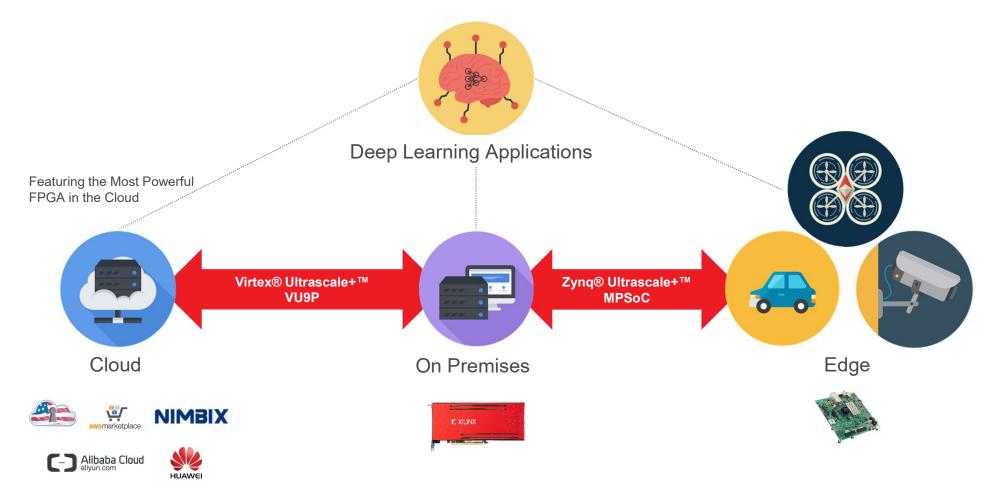

## **Accelerating Al Inference into Your Cloud Applications**

## Xilinx ML Suite - AWS Marketplace

#### > ML Suite

#### >> Supported Frameworks:

- Caffe

- MxNet

- Tensorflow

- Python Support

- Darknet

#### >> Jupyter Notebooks available:

- Image Classification with Caffe

- Using the xfDNN Compiler w/ a Caffe Model

- Using the xfDNN Quantizer w/ a Caffe Model

#### >> Pre-trained Models

- Caffe 8/16-bit

- GoogLeNet v1

- ResNet50

- Flowers102

- Places365

- Python 8/16-bit

- Yolov2

- MxNet 8/16-bit

- GoogLeNet v1

#### >> xfDNN Tools

- Compiler

- Quantizer

https://aws.amazon.com/marketplace/pp/B077FM2JNS

## **Unified Simple User Experience from Cloud to XBB**

Page 6

# Overlay Architecture Custom Processors Exploiting Xilinx FPGA Flexibility

- Customized overlays with ISA architecture for optimized implementation

- Easy plug and play with Software Stack

MLP Engine

Scalable sparse and dense implementation

xDNN – CNN Engine for Large 16 nm

Xilinx Devices

Deephi DPU – Flexible CNN Engine

with Embedded Focus

CHaiDNN – HLS based open source

offering

Deephi ESE LSTM Speech to Text engine

Random Forest Configurable RF classification

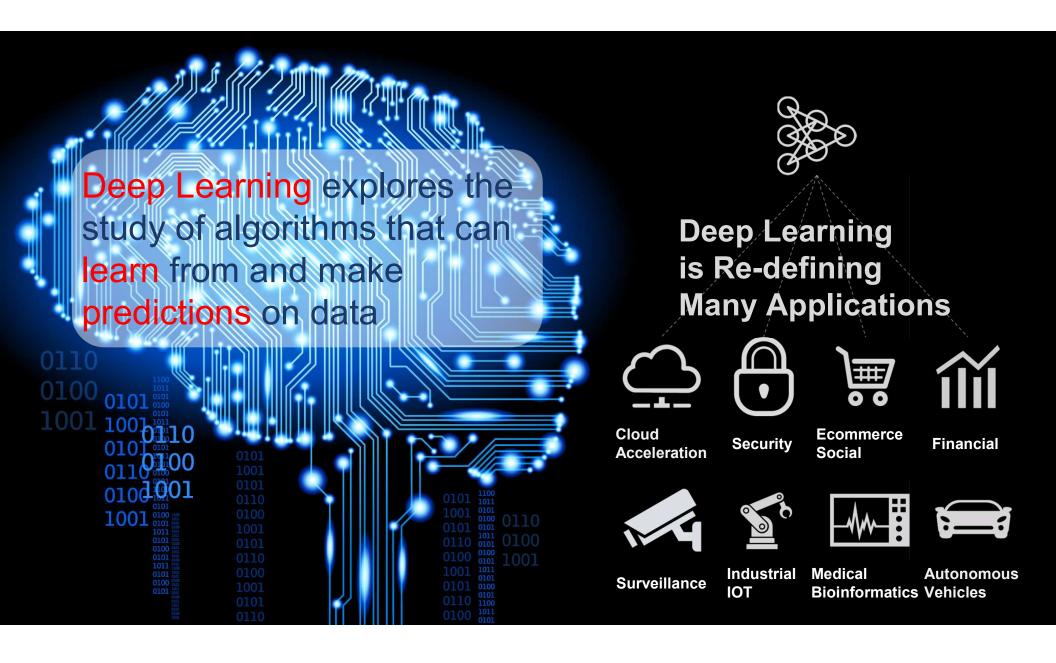

## **Deep Learning Models**

#### Multi-Layer Perceptron

- Classification

- Universal Function Approximator

- Autoencoder

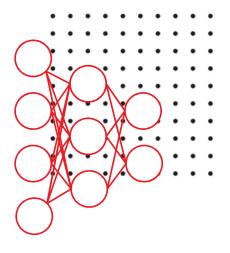

#### Convolutional Neural Network

- Feature Extraction

- Object Detection

- Image Segmentation

#### Recurrent Neural Network

- Sequence and Temporal Data

- Speech to Text

- Language Translation

#### Classification

"Dog"

#### **Object Detection**

#### Segmentation

## Rapid Feature and Performance Improvement

#### >xDNN-v1

- -500 MHz

- URAM for feature maps without caching

- Array of accumulator with

- -16 bit(batch 1), 8 bit(batch 2)

- Instructions: Convolution,Relu, MaxPool,AveragePool,Elementwise

- Flexible kernel size(square) and strides

- Programmable Scaling

- **Q4CY17**

#### >xDNN-v2

- -500 MHz

- -All xDNN-v1 features

- –DDR Caching: LargerImage, CNN Networks

- Instructions: Depthwise Convolution,Deconvolution,Convolution,Transpose Upsampling

- -Rectangular Kernels

- -Q2CY18

#### >xDNN-v3

- -700 MHz

- –Feature compatible with xDNN-v2

- New Systolic ArrayImplementation: 50%Higher FMAX and 2.2xtime lower latency

- Batch of 1 for 8 bit implementation

- Non-blocking Caching and Pooling

- -Q4CY18

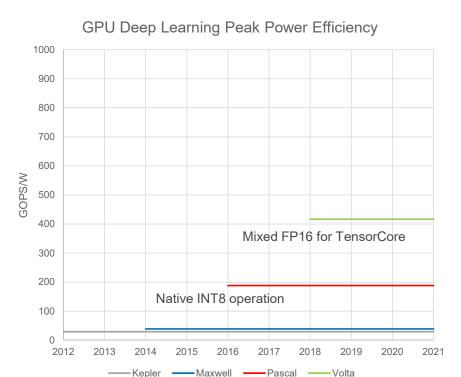

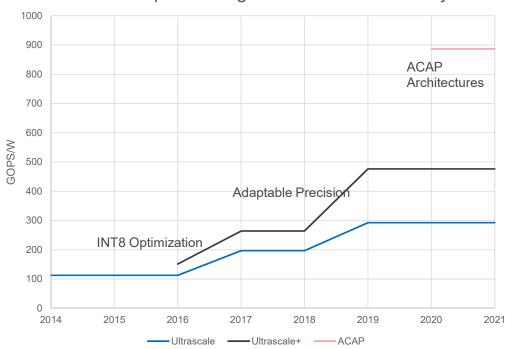

## **Break Through on Peak Performance**

➤ GPU: Introduce new architectures and silicon

➤ Xilinx: Adapt the break through of emerging domain knowledge

FPGA Deep Learning Peak Power Efficiency

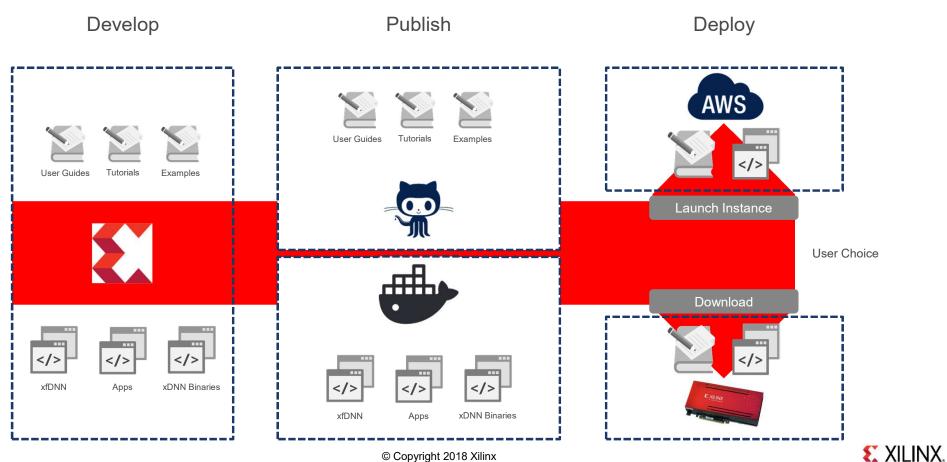

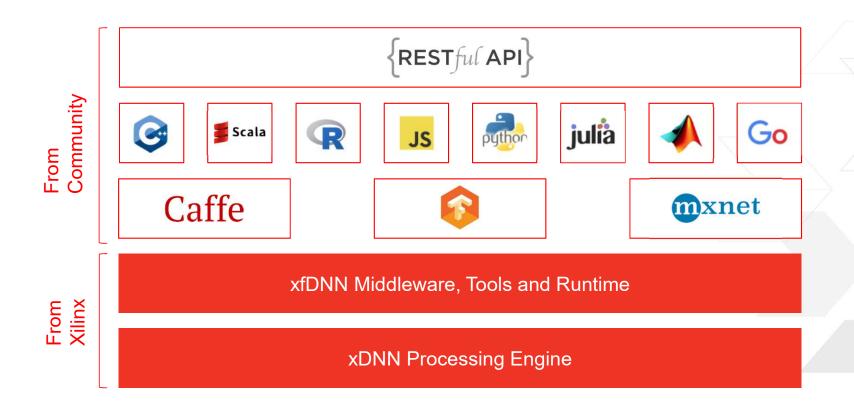

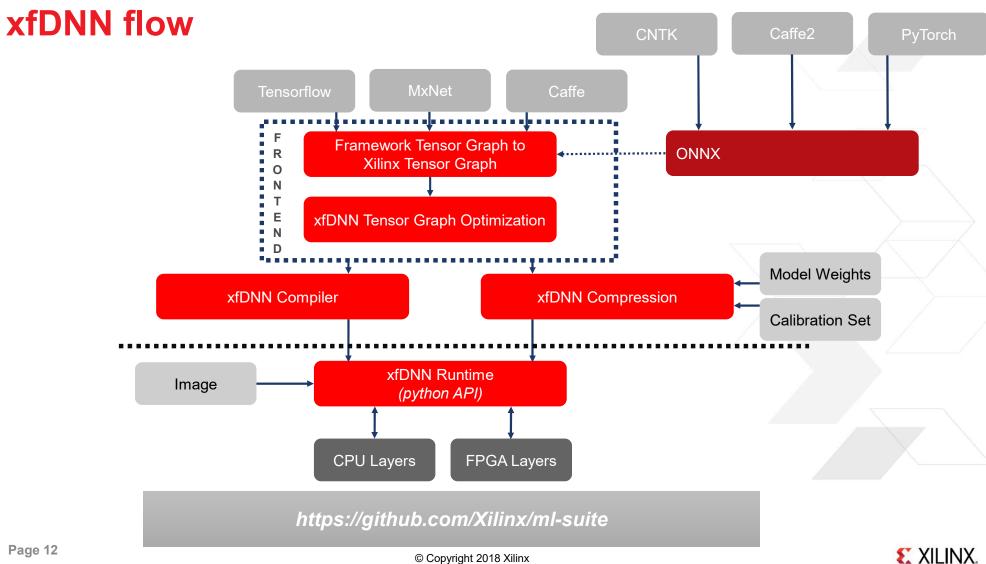

## Seamless Deployment with Open Source Software

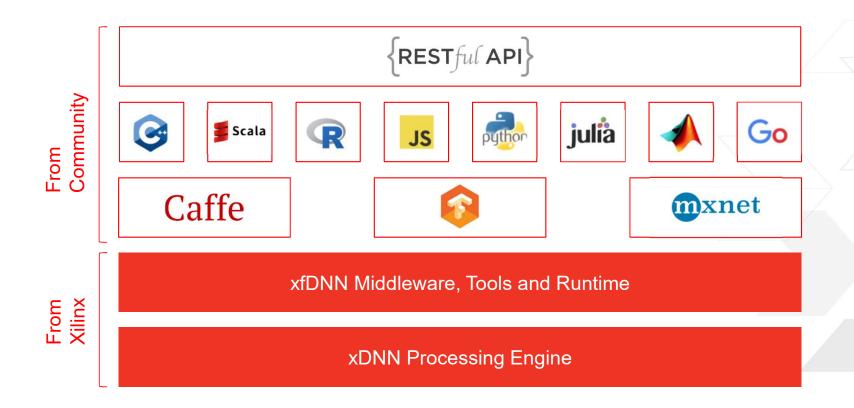

## **xfDNN** Inference Toolbox

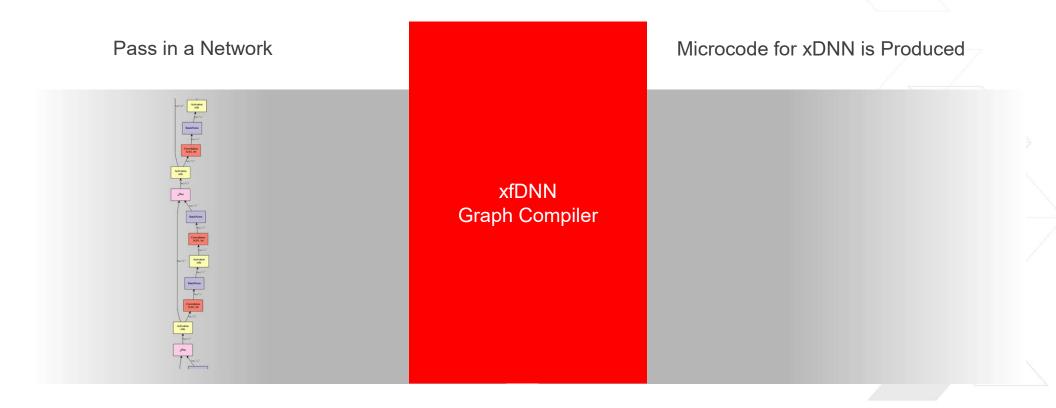

### **Graph Compiler**

Python tools to quickly compile networks from common

Frameworks – Caffe, MxNet and Tensorflow

#### **Network Optimization**

Automatic network optimizations for lower latency by fusing layers and buffering on-chip memory

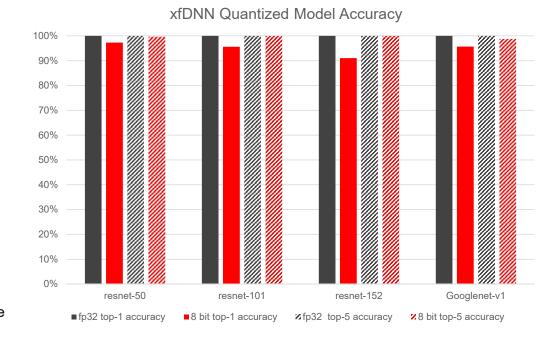

#### xfDNN Quantizer

- Quickly reduce precision of trained models for deployment

- Maintains 32bit accuracy at 8 bit within 2%

## xfDNN Graph Compiler

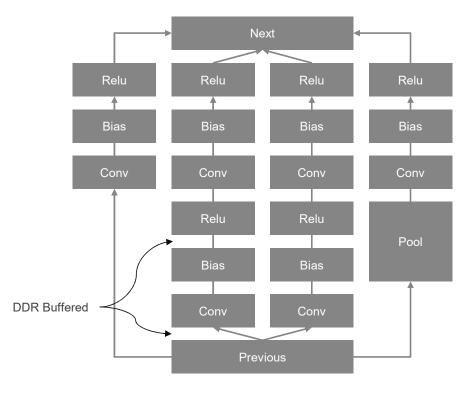

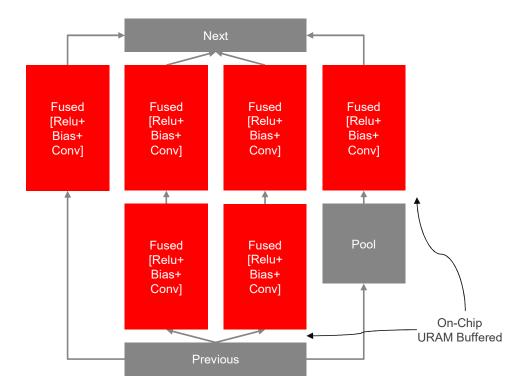

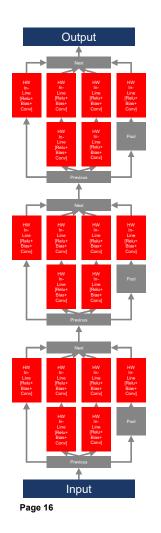

## xfDNN Network Optimization Layer to Layer

**Unoptimized Model**

xfDNN Intelligently Fused layers Streaming optimized for URAM

## xfDNN Network Deployment

#### **Fused Layer Optimizations**

- Compiler can merge nodes

- (Conv or EltWise)+Relu

- Conv + Batch Norm

- Compiler can split nodes

- Conv 1x1 stride 2 -> Maxpool+Conv 1x1 Stride 1

## On-Chip buffering reduces latency and increases throughput

- xfDNN analyzes network memory needs and optimizes scheduler

- For Fused and "One Shot" Deployment

#### "One Shot" deploys entire network to FPGA

- Optimized for fast, low latency inference

- Entire network, schedule and weights loaded only once to FPGA

## xfDNN Quantizer: FP to Fixed-Point Quantization

#### > Problem:

- >> Nearly all trained models are in 32-bit floating-point

- Available Caffe and TensorFlow quantization tools take hours and produce inefficient models

>>

#### Introducing: xfDNN Quantizer

- A customer friendly toolkit that automatically analyses floating-point ranges layer-by-layer and produces the fixed-point encoding that looses the least amount of information

- Quantizes GoogleNet in under a minute

- Quantizes 8-bit fixed-point networks within 1-3% accuracy of 32-bit floating-point networks

- Extensible toolkit to maximize performance by searching for minimal viable bitwidths and prune sparse networks

## xfDNN Quantizer: Fast and Easy

- Provide FP32 network and model

- E.g., prototxt and caffemodel

- 2) Provide a small sample set, no labels required

- 16 to 512 images

- 3) Specify desired precision

- Quantizes to <8 bits to match Xilinx's DSP

## Seamless Deployment with Open Source Software

## Xilinx ML Processing Engine – xDNN

| Features      |                                                              | Description                                    |                                    |  |

|---------------|--------------------------------------------------------------|------------------------------------------------|------------------------------------|--|

|               | Convolution /<br>Deconvolution /<br>Convolution<br>Transpose | Kernel Sizes                                   | W: 1-15; H:1-15                    |  |

|               |                                                              | Strides                                        | W: 1,2,4,8; H: 1,2,4,8             |  |

|               |                                                              | Padding                                        | Same, Valid                        |  |

|               |                                                              | Dilation                                       | Factor: 1,2,4                      |  |

|               |                                                              | Activation                                     | ReLU                               |  |

|               |                                                              | Bias                                           | Value Per Channel                  |  |

|               |                                                              | Scaling                                        | Scale & Shift Value Per<br>Channel |  |

|               | Max Pooling                                                  | Kernel Sizes                                   | W: 1-15; H:1-15                    |  |

| Supported     |                                                              | Strides                                        | W: 1,2,4,8; H: 1,2,4,8             |  |

| Operations    |                                                              | Padding                                        | Same, Valid                        |  |

|               | Avg Pooling                                                  | Kernel Sizes                                   | W: 1-15; H:1-15                    |  |

|               |                                                              | Strides                                        | W: 1,2,4,8; H: 1,2,4,8             |  |

|               |                                                              | Padding                                        | Same, Valid                        |  |

|               | Element-wise Add                                             | Width & Height must match; Depth can mismatch. |                                    |  |

|               | Memory Support                                               | On-Chip Buffering, DDR Caching                 |                                    |  |

|               | Expanded set of image sizes                                  | Square, Rectangular                            |                                    |  |

|               | Upsampling                                                   | Strides                                        | Factor: 2,4,8,16                   |  |

| Miscellaneous | Data width                                                   | 16-bit or 8-bit                                |                                    |  |

- ➤ Programmable Feature-set

- > Tensor Level Instructions

- > 500+MHz DSP Freq (VU9P)

- Custom Network Acceleration

## **Alveo – Breathe New Life into Your Data Center**

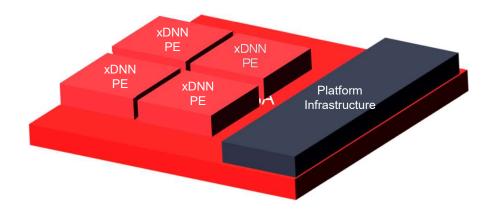

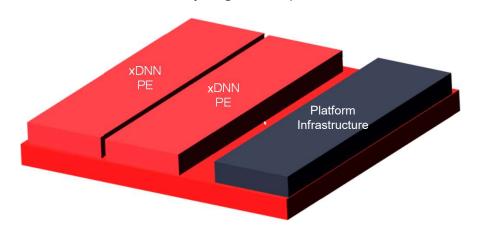

## **ML Suite Overlays with xDNN Processing Engines**

#### **Adaptable** > Al algorithms are changing rapidly > Adjacent acceleration opportunities **xDNN** DDR PΕ xDNN PE Realtime **xDNN** > 10x Low latency than CPU and GPU Platform > Data flow processing **Efficient** CPU > Performance/watt > Low Power

## **xDNN PEs Optimized for Your Cloud Applications**

Throughput, Multi-Network Optimized

Latency, High Res Optimized

| Overlay<br>Name | DSP<br>Array | #PEs | Cache | Precision | GOP/s | Optimized For                        | Examples Networks  |

|-----------------|--------------|------|-------|-----------|-------|--------------------------------------|--------------------|

| Overlay_0       | 28x32        | 4    | 4 MB  | Int16     | 896   | Multi-Network, Maximum<br>Throughput | ResNet50 (224x224) |

| Overlay_1       | 28x32        | 4    | 4 MB  | Int8      | 1,792 | Multi-Network, Maximum<br>Throughput | ResNet50 (224x224) |

| Overlay_2       | 56x32        | 1    | 5 MB  | Int16     | 1,702 | Lowest Latency                       | Yolov2 (224x224)   |

| Overlay_3       | 56x32        | 1    | 5 MB  | Int8      | 3,405 | Lowest Latency                       | Yolov2 (224x224)   |

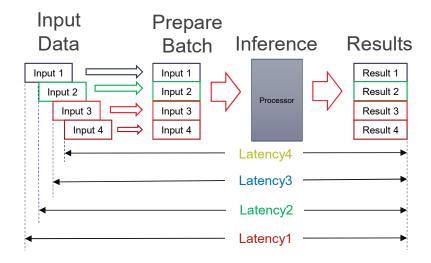

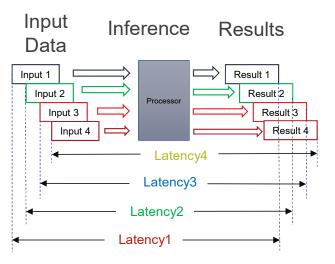

## Real-time Inference

#### Inference with batches

- »Require batch of input data to improve data reuse and instruction synchronization

- >> High throughput depends on high number of batch size

- »High and unstable latency

- >> Low compute efficiency while batch is not fully filled or at lower batch size © Copyright

#### > Real Time Inference

- No requirement for batch input data

- Throughput less related to batch size

- Low and deterministic latency

- Consistent compute efficiency

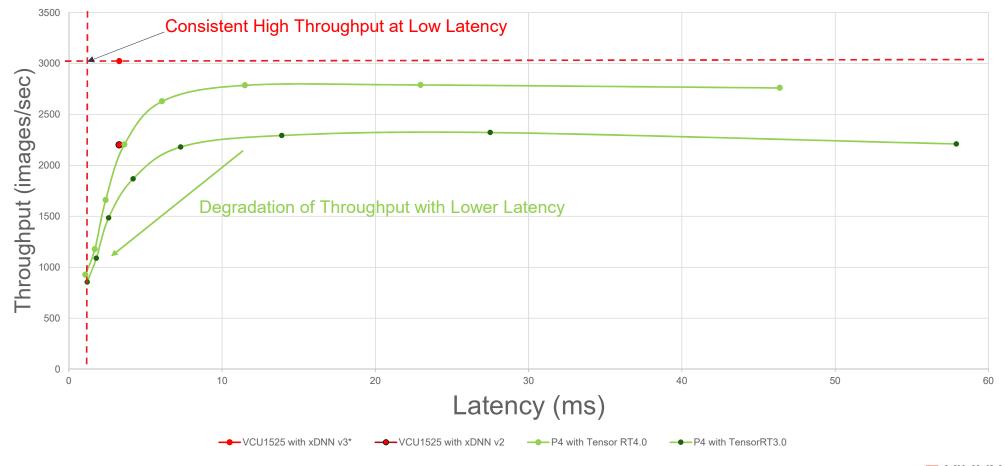

## Xilinx - High Throughput at Real-Time

GoogLeNet V1 Performance

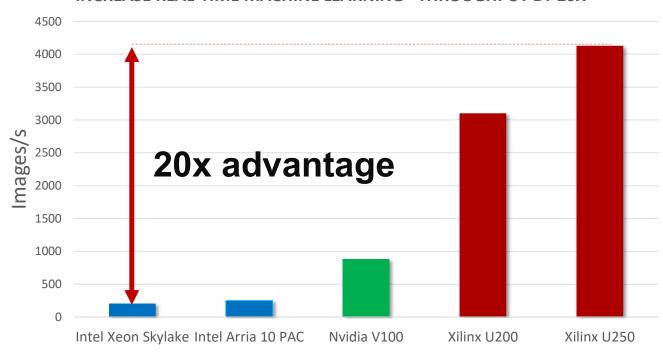

# Fast Advantages in Machine Learning Inference

#### **INCREASE REAL-TIME MACHINE LEARNING\* THROUGHPUT BY 20X**

<sup>\*</sup> Source: Accelerating DNNs with Xilinx Alveo Accelerator Cards White Paper

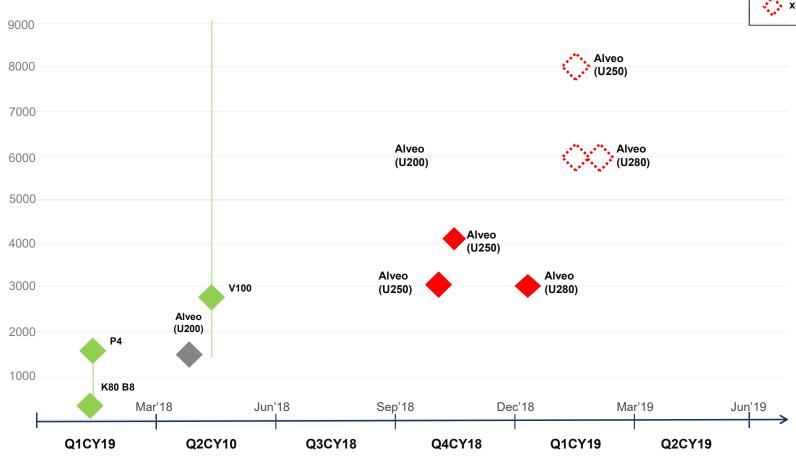

## **ML Suite Performance Roadmap**

Page 27

## Visit Xilinx.com/ML for more information

https://www.xilinx.com/applications/megatrends/machine-learning.html

# Adaptable. Intelligent.