Vitis Solver Library

- Design Tools

- Vitis Unified Software Platform

- Vitis Libraries

- Vitis Solver Library

The Vitis™ Solver library offers a collection of performance-optimized matrix decomposition, linear/eigen value solvers, and other functions that can be used for designing accelerated algorithms for RADAR, LiDAR, computer vision, computational finance, and other applications.

Vitis Solver library kernels can be used as standalone accelerators that you can call in your embedded/host CPU code or combine with other Vitis library kernels and primitives to accelerate your end-to-end processing pipeline.

Some of the key accelerated functions currently available include Singular Value Decomposition (SVD), QR & LU (lower-upper) Decomposition, Matrix Inverse, Triangular Solvers, Eigen Value Decomposition, and others.

Vitis Solver Library – Functions

Currently, the Vitis Solver library includes the following operations for dense matrixes:

Matrix decomposition

- Cholesky decomposition for symmetric positive definite matrixes

- LU decomposition without pivoting and with partial pivoting

- QR decomposition for general matrixes

- SVD (single value decomposition) for symmetric and non-symmetric matrixes (Jacobi method)

Linear solver

- Tridiagonal linear solver (parallel cyclic reduction method)

- Linear solver for triangular matrixes

- Linear solver for symmetric and non-symmetric matrixes

- Matrix inverse for symmetric and non-symmetric matrixes

Eigenvalue solver

- Jacobi eigenvalue solver for symmetric matrixes

Programmable Logic (PL) & AI Engine (AIE) Arrays Functions List

The Vitis Solver library targets Vitis kernel developers to help accelerate their application development. The library provides two layers of APIs, namely L1 and L2. The L1 and L2 functions are listed in the table below.

The Vitis Solver library 2022.2 release added two new AI Engine functions: QR Decomposition and Cholesky Decomposition.

| Solver Library Functions | |

|---|---|

| L1 | QR (Quadrature Rotation) Decomposition |

| QR_Inverse | |

| SVD (Singular Value Decomposition) | |

| Cholesky_Inverse | |

| Cholesky Decomposition | |

| QR Decomposition for AIE | |

| Cholesky Decomposition for AIE | |

| L2 | Matrix Decomposition |

| Eigenvalue Solver | |

| Linear Solver | |

Features of the L1 and L2 APIs are described below.

| L1 APIs | Functions for matrix decomposition. Designed as HLS components with memory interfaces (pointing to BRAM or URAM). These APIs support a variety of data types, including float, double, or complex. Since L1 APIs need all input data ready in memory, they do have an upper limit to the total size of the input matrix. |

|---|---|

| L2 APIs | Kernels running on the FPGA devices. These APIs support double-precision, floating-point types. They read DDR/HBM to get input and write DDR/HBM to output results. They can be called from the host side. |

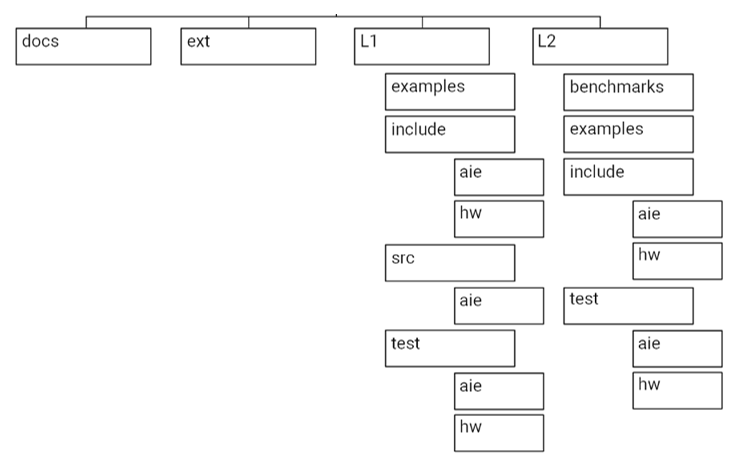

Organization

The Vitis Solver library is organized into L1 and L2 folders, each relating to a different stage of application development.

L1: Makefiles and sources in L1 facilitate an HLS-based flow for quick checks.

L2: Makefiles and sources in L2 facilitate building the XCLBIN file from various sources (HDL, HLS, or XO files) of kernels with the host code written in an OpenCL™/XRT framework targeting a device.