# **Tips and Tricks for IP Integrator**

**Presented By**

Daniel E. Michek Interaction Design 16 October, 2018

## **The Evolution of IP Integrator**

2013 - IPI

debut –

**IP** Integrator

replaces XPS

### 2015 - HLx

Vivado HLx Methodology –

IP Integrator for shell

SDx / HLS for differentiation

#### Next – ACAP

#### Versal ACAP debut –

IP Integrator enables H/W shell with Versal heterogeneous features

IP Integrator improves WYSIWYG RTL

# What You'll See in this Presentation

### > Technical, demo centric, methodology tips presentation

- >> Helpful today

- >> Needed for tomorrow

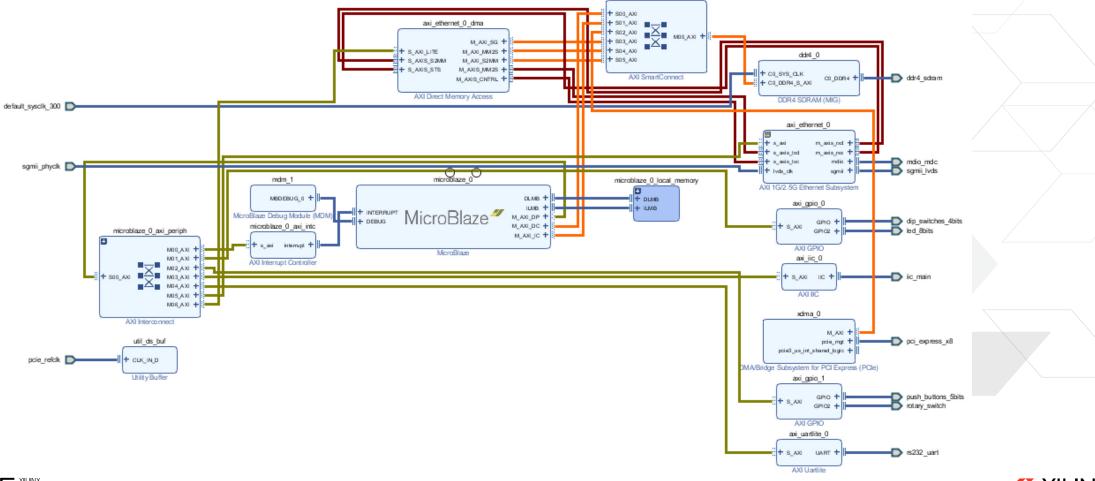

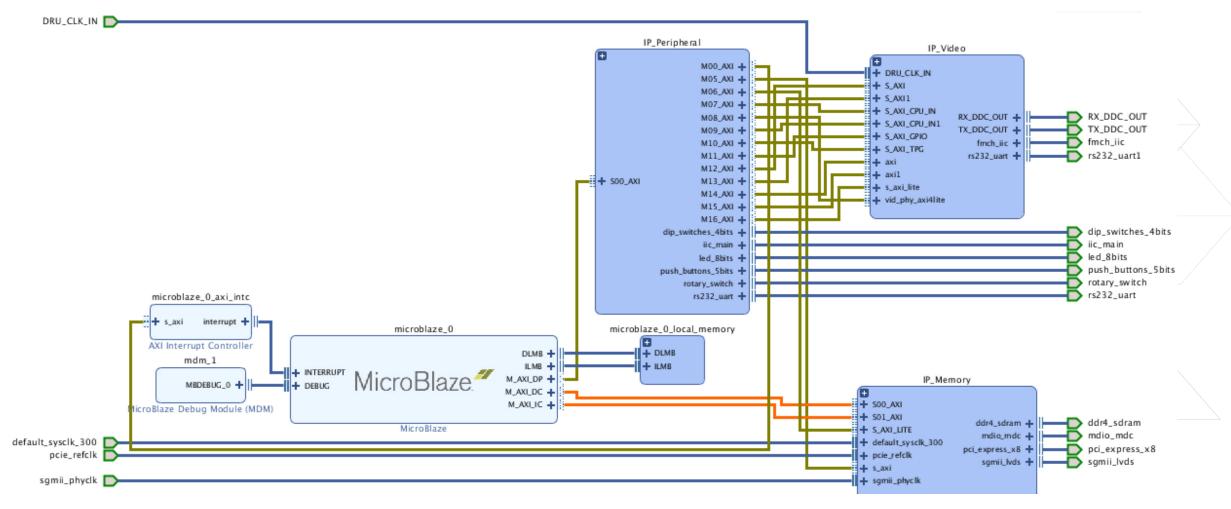

### > We'll see, using a real-world design

- >> Features of IP Integrator to rapidly build designs with complex IP

- >> New Ease-of-Use features (Find, Pinning)

- >> New Design Migration capabilities

- >> New Design Differencing

# **Most Common Requests for IP Integrator**

#### > Ease-of-Use

- >> Finding IP, Freezing IP

- >> Example Designs in IP Integrator

#### > Migration Hurdles

- >> Selectively updating IP

- >> Migrating to next generation devices

#### > Team Based Design

- >> Enable teams to work in tandem (Spring 2019)

- >> Visualize differences between Block Diagrams

## **Visual Walkthrough**

### > Start to End

- 1. Creating a new design for the KCU105

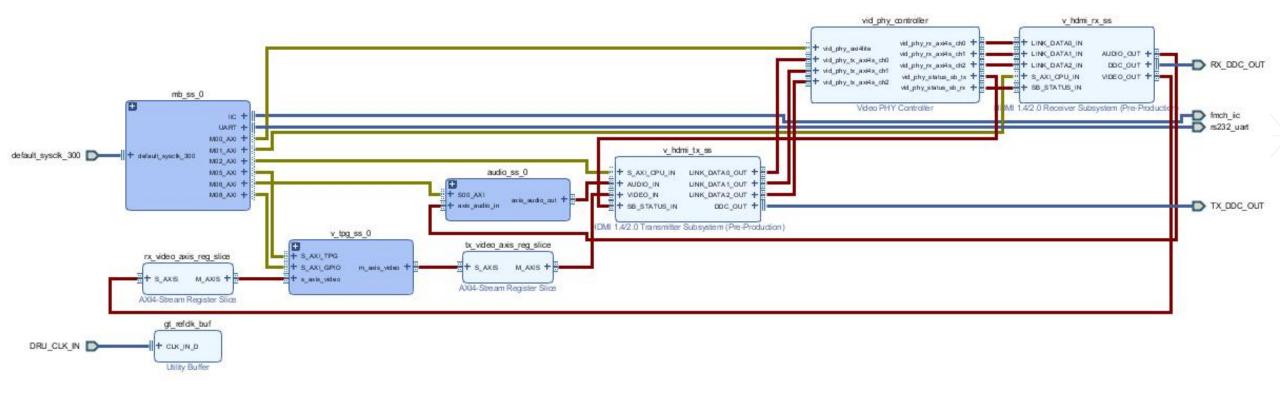

- 2. Creating an example design for HDMI

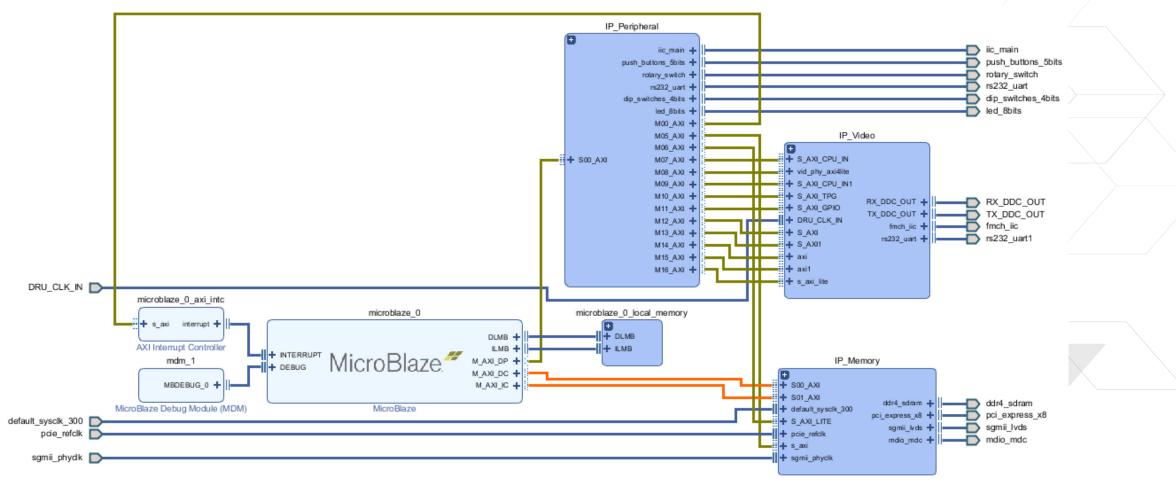

- 3. Using Find and hierarchical partitioning

- 4. Migrating from ProjectA.bd to ProjectB.bd

- 5. Cross Probing with timing closure

- 6. The toolbar review

- --- 2018.3 Preview ----

- 7. Selective migration from Vivado 2018.1 to 2018.3

- 8. What changed during upgrade in the block diagram

- 9. Migrating to the Versal NoC

### **1. Ease of Use – Designer Assistance**

XILINX DEVELOPER FORUM

© Copyright 2018 Xilinx

**EXILINX**.

## **2. Example – Example Designs**

> Example Designs can be launched from IP Integrator or IP Catalog

### 3. Ease of Use – "Super Find" in IP Integrator

#### > Find items on the canvas based on connectivity, naming, or properties

| ind Find                                                                    | X   |

|-----------------------------------------------------------------------------|-----|

| Find objects by filtering Tcl properties and objects.                       | 4   |

| Result name: axis_blocks ⊗<br>Eind: Block ✓<br>Properties                   |     |

| NAME V contains V *                                                         |     |

| ■ <u>Regular expression</u> <u>Ignore case</u> <u>Search hierarchically</u> |     |

| Of objects:                                                                 |     |

| Command: show_objects -name axis_blocks [get_bd_cells -hierarchical ***]    |     |

| ✓ Open in a new tab                                                         |     |

| OK Can                                                                      | cel |

© Copyright 2018 Xilinx

## 4. Migration – From One Block Diagram to Another

#### > Block diagrams should be in the same project

**E** XILINX.

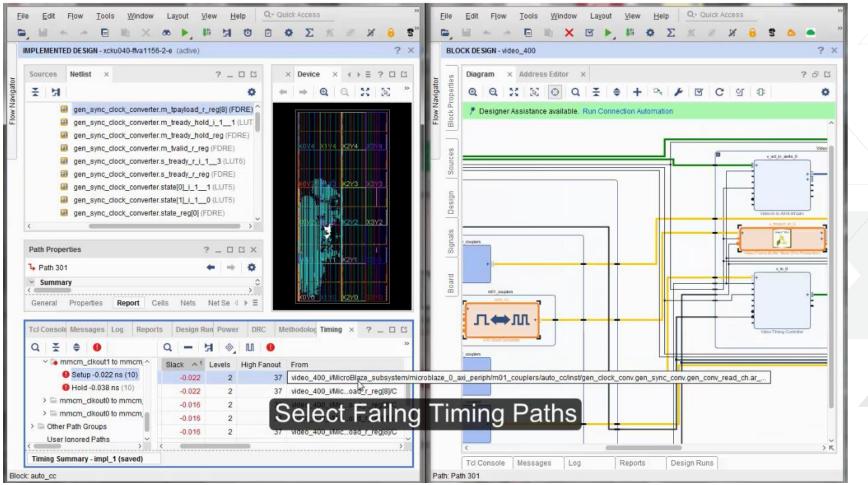

### 5. Ease of Use – Cross Probe from Timing Analysis

#### > Quickly find areas that need improvement

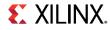

### 6. Ease of Use – Stop Squirming - Pin IP on Canvas

> A review of the toolbar actions

© Copyright 2018 Xilinx

# A Preview of IP Integrator's Migration Assistance in 2018.3

© Copyright 2018 Xilinx

# **Visual Walkthroughs**

### > Start to End

- 1. Creating a new design for the KCU105

- 2. Creating an example design for HDMI

- 3. Using Find and hierarchical partitioning

- 4. Migrating from ProjectA.bd to ProjectB.bd

- 5. Cross Probing with timing closure

- 6. The toolbar review

- --- 2018.3 Preview ----

- 7. Selective migration from Vivado 2018.1 to 2018.3

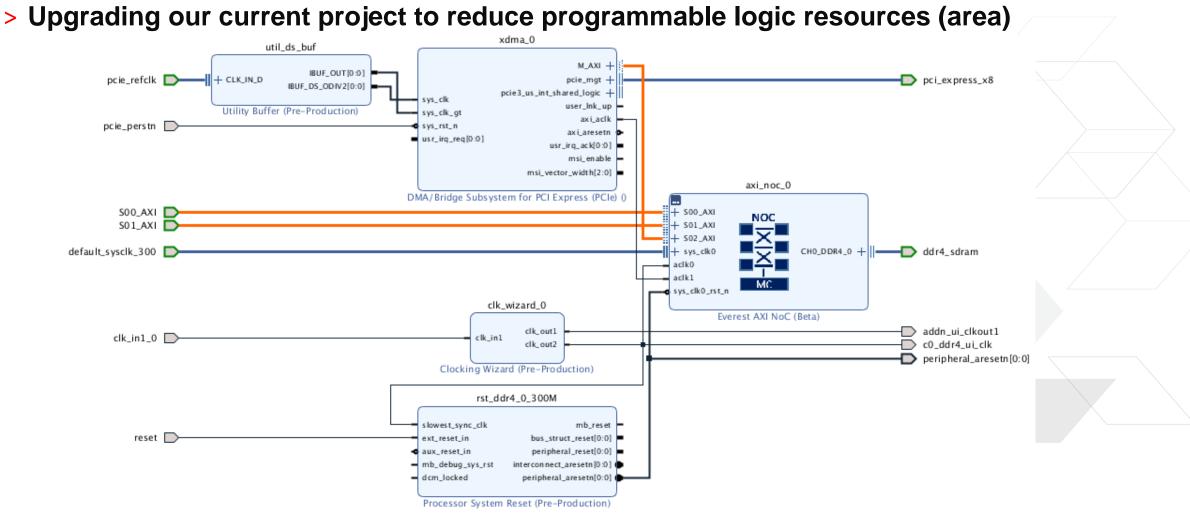

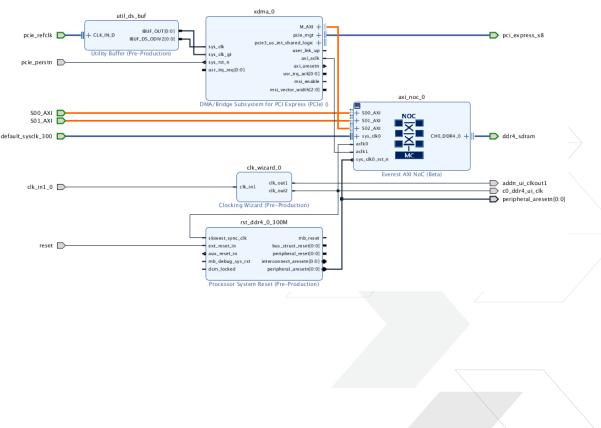

- 8. What changed during upgrade in the block diagram

- 9. Migrating to the Versal NoC

## 7. Migration – Vivado Versions via Partial Update

> Keep the blocks which have been previously validated in-system

**E** XILINX.

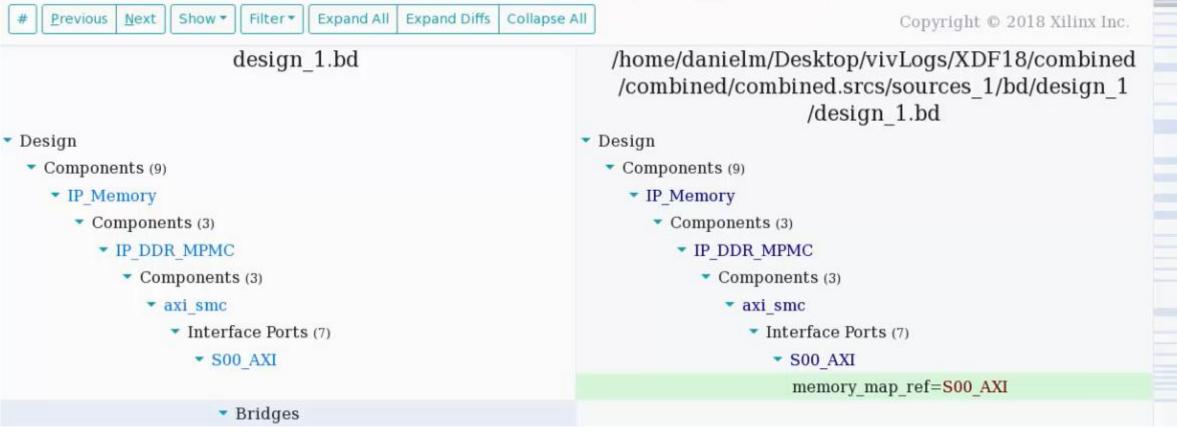

# 8. What Changed In the Upgrade?

DEVELOPER

#### > New interactive report shows differences between block diagrams

### **Block Diagram Differences**

© Copyright 2018 Xilinx

**EXILINX**

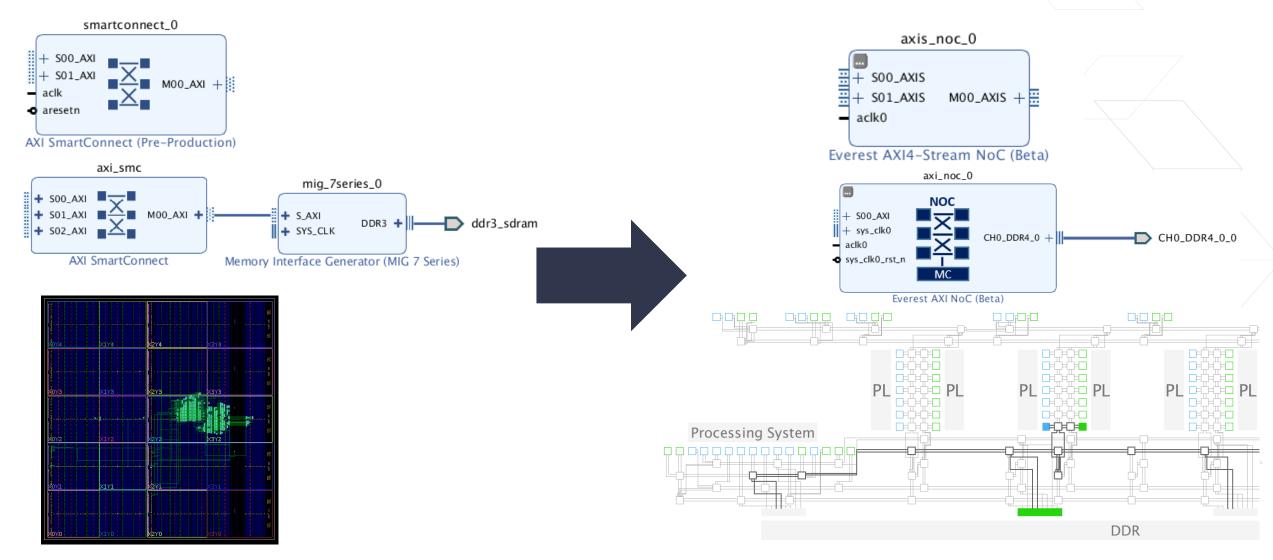

### **Preview: Versal NoC!**

The veloper of the veloper forum

© Copyright 2018 Xilinx

**E** XILINX.

# 9. Migrating to Versal ACAP

© Copyright 2018 Xilinx

**E** XILINX.

# **Most Common Requests for IP Integrator**

#### > Ease-of-Use

- >> Finding IP, Freezing IP

- >> Example Designs in IP Integrator

### > Migration Hurdles

- >> Selectively updating IP

- >> Migrating to next generation devices

### > Team Based Design

- >> Enable teams to work in tandem (Spring 2019)

- >> Visualize differences between Block Diagrams

**E** XILINX

## **Changes to Our Release Schedule**

#### > Vivado previously had four full releases per year

- >> 2017.1 & 2017.3 introduced new features

- >> 2017.2 & 2017.4 improved quality Many users installed only the even releases

#### > In 2018, we will have three full releases

>> 2018.3 is coming soon

#### > And two in 2019

- >> Spring and Fall No more wait states for new features or quality

- >> Quality is our top priority

# **Key Concepts: Vivado IP Integrator 2018.3**

# Board, Block, Connectivity, and Migration Assistance

> Take advantage of IP Integrator's built in assistance to create your ideal processing system -- including adding customized interfaces for networking, video, and DSP

# Getting ready to migrate to Versal ACAP

> The migration to Versal ACAP will continue to add new assistance features and increase the traceability of IP Integrator

### XILINX DEVELOPER FORUM

© Copyright 2018 Xilinx