## Vivado Synthesis Tips & Tricks

Presented By

Balachander Krishnamurthy Sr. Product Marketing Manager October 2<sup>nd</sup>, 2018

## **Topics for Today**

> The UltraFast Design Methodology

> UFDM: Customer Case Study

> Waiver Mechanism

> Vivado Incremental Synthesis

> QoR: Tips & Tricks

# UltraFast Design Methodology

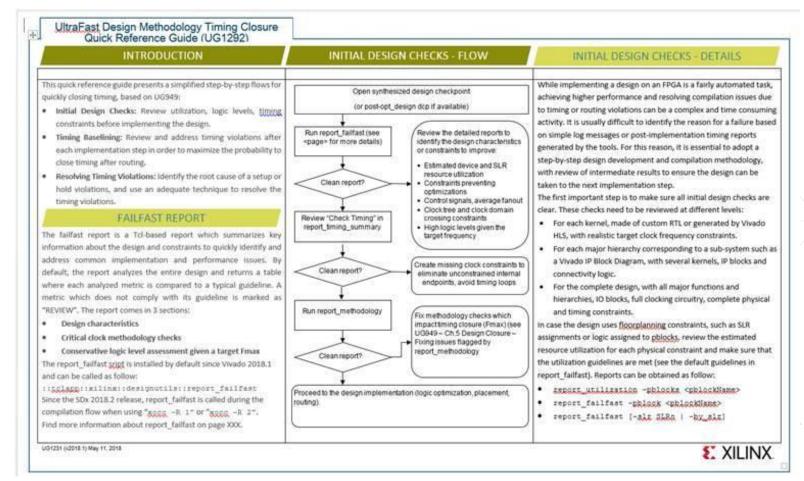

## UEW UG1292: UFDM Timing Closure Quick Reference Card

- Step-by-step Analysis and Suggestions

- Address common timing closure challenges

- >> HLx and SDx

- >> Project and Non-project

https://www.xilinx.com/support/documentation/sw\_manuals/xilinx2018\_2/ug1292-ultrafast-timing-closure-quick-reference.pdf

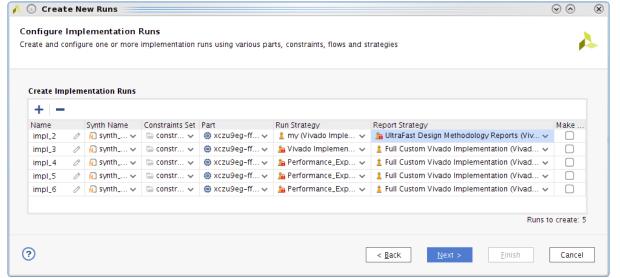

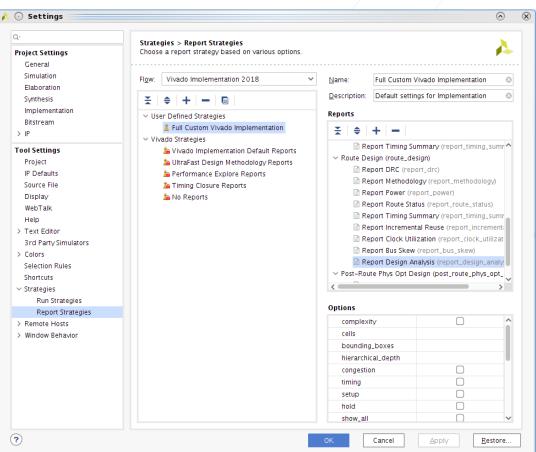

### Report Run Strategies

Create custom report strategies similar to custom run strategies

- > Improve compile time

- >> Select which reports are generated for each run

- >> Configure options for each report individually

> Reuse report strategies across runs and projects

## **UFDM: Customer Case Study**

### **Customer Case Study: Design not functional**

- > Major Xilinx customer with tight production deadline

- > Customer claimed

- >> Running 'place\_design -fanout\_opt' caused functional issue

- >> Adding ILA to DCP, design issue is gone

- >> Not a CDC issue

- > OneSpin equivalency checking is clean

- >> opt\_design DCP compared with place\_design DCP

> SR filed and escalated to factory

### **Customer Case Study: Analysis by factory**

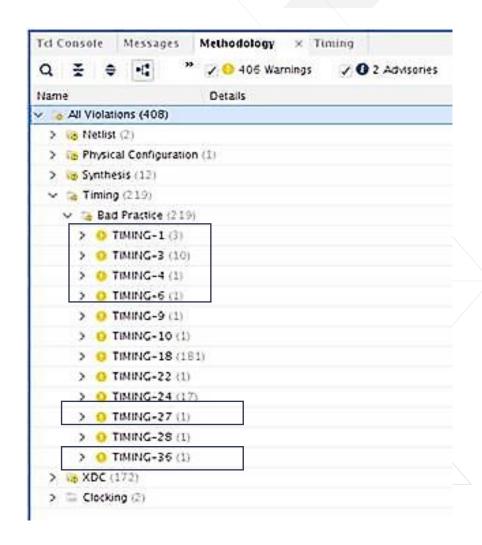

#### > Many UltraFast Methodology Violations

- >> Timing -1 → Incorrect clock waveform

- >> Timing-3 → Breaking clock propagation delay and potentially skew accuracy

- >> Timing-6, 27 → Primary clock defined on hierarchical pin

- >> Timing-36 → Inaccurate skew due to missing insertion delay on a generated clock

## Customer Case Study: Analysis by factory ...2

#### > Report CDC flagged ~10K Critical violations!

| Severity ^1 | ID     | Count | Description                                        |

|-------------|--------|-------|----------------------------------------------------|

| Oritical    | CDC-1  | 8823  | 1-bit unknown CDC circuitry                        |

| O Critical  | CDC-4  | 28    | Multi-bit unknown CDC circuitry                    |

| O Critical  | CDC-7  | 335   | Asynchronous reset unknown CDC circuitry           |

| O Critical  | CDC-10 | 1089  | Combinational logic detected before a synchronizer |

| O Critical  | CDC-11 | 247   | Fan-out from launch flop to destination clock      |

| O Critical  | CDC-13 | 681   | 1-bit CDC path on a non-FD primitive               |

| O Critical  | CDC-14 | 8     | Multi-bit CDC path on a non-FD primitive           |

| Warning     | CDC-2  | 478   | 1-bit synchronized with missing ASYNC_REG property |

Waivers can help focus on new or un-reviewed issues

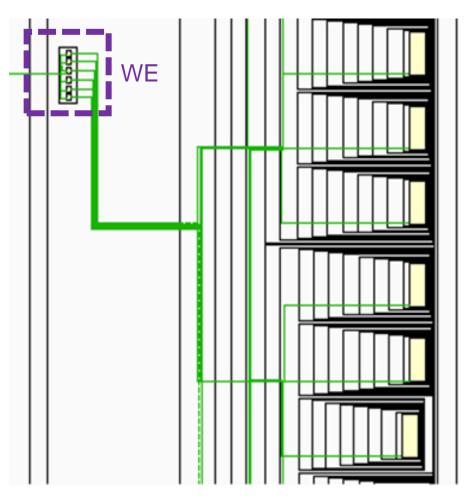

### > CDC-11 violations introduced by placer fanout opt

- User allowed replication of CDC endpoint (RAMB/WE control signal)

- => RAMBs written in different cycles

Safe CDC topology would have prevented replication

#### > Outcome

Design working after addressing methodology and CDC violations

## Waiver Mechanism

#### **Waiver Mechanism**

- > Hide violations in CDC/DRC/Methodology checks in the design

- >> Focus only on what is relevant

- > Waivers can be created, queried, reported against and deleted

- >> Track user, timestamp and description

- >> Waivers should be reviewed by the design team

- >> XDC Compatible, allows read/write and scoping

- >> Duplicate waivers ignored

- > Recommend

- >> Don't waive Critical violations

- >> Waive Warning (after reviewing them) and Info types

- > Xilinx IPs have adopted waiver mechanism

- > Documentation

- >> UG906: Design Analysis and Closure Techniques

- >> UG938: Tutorial Design Analysis and Timing Closure (NEW)

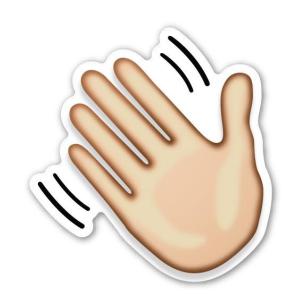

### **Creating a Waiver**

> Create from: Report CDC / DRC / Methodology result window

> Create from: CDC / DRC / Methodology violation objects

```

report_cdc -name cdc_1

foreach vio [get_cdc_violations -name cdc_1 -filter {CHECK == CDC-1}] {

if {[regexp {^top/sync_1} [get_property STARTPOINT_PIN $vio]]} {

create_waiver -of $vio -description {Safe by protocol}

}

}

```

Notice: only description argument specified with this method.

- > Create from: manual specification of all arguments

- >> Arguments are order dependent. They must match order inside the violation object

### **Reporting Waivers**

- In Report CDC / DRC / Methodology GUI (and command line)

- >> Report can be generated with the waivers

- >> Report can be generated by ignoring the waivers

- >> Can report only waived violations

- > report\_waivers

- Only Text Based

- >> GUI Support coming soon

- Report CDC/DRC/Methodology must be run prior to extract statistics

#### **Useful Waiver Commands**

create\_waiver

get\_waivers

delete\_waivers

write\_waivers

report\_waivers

# Vivado Incremental Synthesis

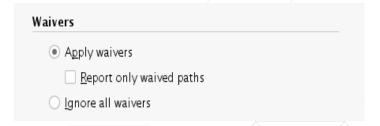

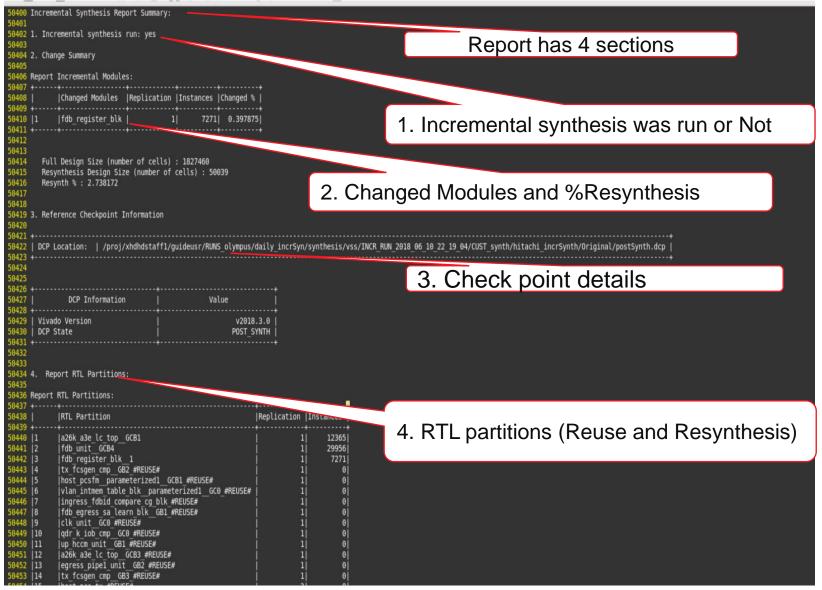

### **NEW** Incremental Synthesis

#### > Flow similar to incremental P & R

#### > Benefits:

- >> 40% synthesis runtime reduction

- Change is localized

- >> Iterate quickly while working on a module

- >> More design iterations in the front end

- >> Improved predictability in results

- >> Fewer changes in netlist structure when compared to previous flow

- >> Improved results/QoR/runtime when used with Incremental P & R

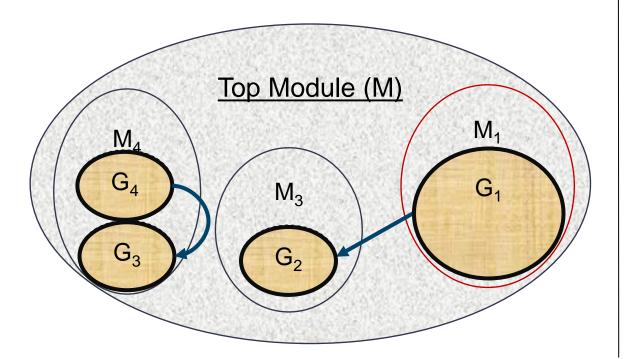

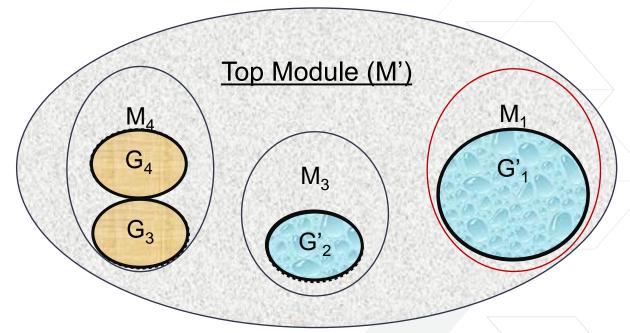

### Incr. Synthesis - Cross-Boundary Optimizations

#### Reference Run

Track cross-boundary optimizations

#### **Incremental Run**

Re-synthesize changed modules + its dependencies

- > More cross boundary optimizations leads to more re-synthesis (G'1 → G'2)

- > Changed / dissolved partitions also need to be re-synthesized

### Log file and Non-Project Mode Flow

#### > Reference run

- >> run.tcl

- synth\_design

- write\_checkpoint –incremental\_synth force postSynth.dcp

- opt\_design

- place\_design

- Phys-opt\_design ← optimizations1

- route\_design

- write\_checkpoint routed.dcp

- Phys-opt\_design ←optimizations2

- write\_checkpoint ref\_run\_postroute\_physopt.dcp

#### Incremental run

- >> run.tcl

- read\_checkpoint –incremental../ReferenceRunDir/postSynth.dcp

- synth\_design

- write\_checkpoint –incremental\_synth force postSynth\_incr.dcp

- opt\_design

- read\_checkpoint –incremental ../ReferenceRunDir/ref\_run\_postroute\_physopt.dcp ← optimizations1 + optimizations2

- place\_design

- route\_design

- write\_checkpoint routed\_incr.dcp

## QoR: Tips & Tricks

### **Tips and Tricks: ROM Optimization**

```

process(clk)

variable AB xor: std logic vector(63 downto 0);

variable Box1, Box2, Box3, Box4, Box5, Box6, Box7, Box8, Box9, Box10: std_logic_vector(3 downto 0);

variable BoxAll, Box xor: std logic vector(39 downto 0);

begin

if (clk = '1' and clk'event) then

AB xor:=inA(i) xor inB(i);

64-deep ROM, 4-bit wide accessing different locations

Box1:=Box(conv integer(AB xor(63 downto 58)));

Box2:=Box(conv integer(AB xor(57 downto 52)));

Loop with 30 iterations

Box3:=Box(conv integer(AB xor(51 downto 46)));

10 ROM structures per iteration (300 ROMs in total)

Box4:=Box(conv integer(AB xor(45 downto 40)));

Box5:=Box(conv integer(AB xor(39 downto 34)));

Data in 0-15 repeated in 16-31. 32-47 and 48-62

Box6:=Box(conv integer(AB xor(33 downto 28)));

Could this be 16 deep instead of 64 deep?

Box7:=Box(conv integer(AB xor(27 downto 22)));

Box8:=Box(conv integer(AB xor(21 downto 16)));

Box9:=Box(conv integer(AB xor(15 downto 10)));

Box10:=Box(conv integer(AB xor(9 downto 4)));

BoxAll:=Box1 & Box2 & Box3 & Box4 & Box5 & Box6 & Box7 & Box8 & Box9 & Box10;

Box xor:=BoxAll xor inA(i)(63 downto 24) xor inB(i)(39 downto 0);

outA(i) \le Box xor \& inA(i)(23 downto 0);

outB(i) \le inB(i);

end if:

end process;

```

Missing uniformity in ROM data => 64th location

### **Tips and Tricks: ROM Optimization**

```

process(clk)

variable AB xor: std logic vector(63 downto 0);

variable Box1, Box2, Box3, Box4, Box5, Box6, Box7, Box8, Box9, Box10: std logic vector(3 downto 0);

variable BoxAll, Box xor: std logic vector(39 downto 0);

begin

if (clk = '1' and clk'event) then

AB xor:=inA(i) xor inB(i):

if(AB xor(63 downto 58) = "1111111") then

Box1:= "0000";

Box1:=Box(conv integer(AB xor(63 downto

end if:

if(AB xor(57 downto 52) = "1111111") then

Box2:= "0000":

Check the condition to access the data for address#63

else

Box2:=Box(conv integer(AB xor(57 downto 52)));

end if:

if(AB xor(51 downto 46) = "111111") then

Box3:= "0000";

The ROM now can become 16-deep and 4-bit wide

Box3:=Box(conv integer(AB xor(51 downto 46)));

end if:

```

|                                          | <u>.</u>         |          |                    |                  |                                              |                |          |                    |            |

|------------------------------------------|------------------|----------|--------------------|------------------|----------------------------------------------|----------------|----------|--------------------|------------|

| Site Type                                | Used             | Fixed    | Available          | Util%            | Site Type                                    | ++<br>  Used   | Fixed    | +<br>  Available   | +          |

| ice LUTs*<br>LUT as Logic                | 3087             | 0 0      | 303600<br>303600   | 1.02  <br>  1.02 | Slice LUTs*                                  | 1826           | 0        | 303600             | <u>+</u> - |

| LUT as Memory LUT as Distributed RAM     | 4                | 0        | 130800             | <0.01            | LUT as Logic                                 | 1822  <br>  4  | 0        | 303600<br>303600   | l          |

| LUT as Shift Register                    | 4                | 0        | <br>               |                  | LUT as Distributed RAM LUT as Shift Register | 0              | 0<br>  0 | <br>               | <br>       |

| Slice Registers<br>Register as Flip Flop | 3981  <br>  3981 | 0        | 607200<br>607200   | 0.66  <br>0.66   | Slice Registers<br>  Register as Flip Flop   | 3981  <br>3981 | 0<br>  0 | 607200<br>607200   | l          |

| Register as Latch<br>F7 Muxes            | 0  <br>  0       | 0<br>  0 | 607200<br>  151800 | 0.00  <br>  0.00 | Register as Latch<br>  F7 Muxes              | 0 0            | 0<br>1 0 | 607200<br>1 151800 | Ì          |

| F8 Muxes                                 | 0                | 0<br>    | 75900<br>+         | 0.00             | F8 Muxes                                     | j 0 j          | 0        | 75900              | İ          |

LUT difference = Original - Proposed (3087 - 1826) = 1261

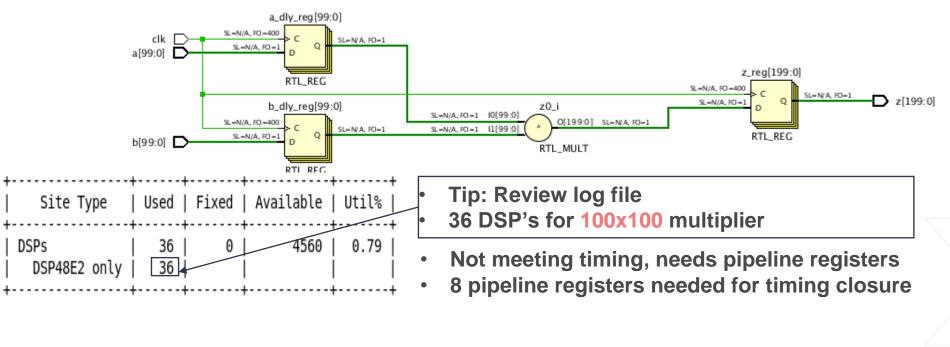

## Tips and Tricks: 500 MHz Wide Multiplier

warning, raiarier synchesis criceria is noc mec

Total Number of Endpoints:

INFO: [Synth 8-5845] Not enough pipeline registers after wide multiplier. Recommended levels of pipeline registers is 36 [/archive/marketing\_designs/balacha/customer\_di

Total Number of Endpoints:

#### **Design Timing Summary** Setup Hold Pulse Width Worst Negative Slack (WNS): Worst Pulse Width Slack (WPWS): 0.532 ns 0.162 ns Worst Hold Slack (WHS): 0.016 ns Total Negative Slack (TNS): 0.000 ns Total Hold Slack (THS): 0.000 ns Total Pulse Width Negative Slack (TPWS): 0.000 ns Number of Failing Endpoints: Number of Failing Endpoints: Number of Failing Endpoints:

1547

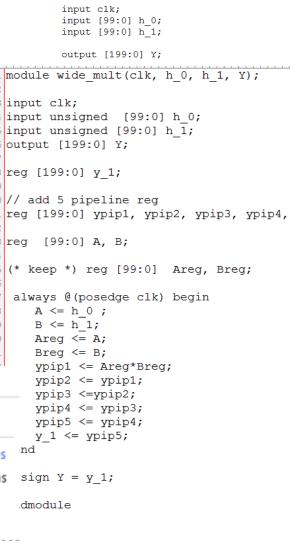

//wide multiplier

module wide mult(clk, h 0, h 1, Y);

Total Number of Endpoints

## Tips and Tricks: Multiplier => LUT mapping

- > Higher utilization v/s competition for multipliers

- > Need to compare LUT based mapping

- >> Map to DSP (use\_dsp48 = "no")

- Convert to LUT based (-max\_dsp 0)

#### With -max\_dsp 0

| CLB LUTs*                        | Site Type                                                                                        | Used                                  | Fixed                 | Available                                                            | Util%                                                  |

|----------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|----------------------------------------------------------------------|--------------------------------------------------------|

| 1 1 3 MUNCS 1 0 1 30320 1 0.00 1 | LUT as Logic LUT as Memory CLB Registers Register as Flip Flop Register as Latch CARRY8 F7 Muxes | 13206<br>0<br>979<br>979<br>0<br>1474 | 9<br>9<br>9<br>9<br>9 | 788160<br>394560<br>1576320<br>1576320<br>1576320<br>98520<br>394080 | 1.68  <br>0.00  <br>0.06  <br>0.06  <br>0.00  <br>1.50 |

#### With use\_dsp48 = "no" attribute

| A         |                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------|

| CLB LUTs* | 60   1.33  <br>60   0.00  <br>20   0.03  <br>20   0.03  <br>20   0.00  <br>20   0.70  <br>80   0.00  <br>40   0.00 |

### **Summary**

> Following the UltraFast Design Methodology reduces Time-to-Market

> Waiver Mechanism for CDC, Methodology and DRCs enables clean reports and design sign-off

- > Ensure Clock Domain Crossing issues are reviewed and fixed

- >> Use the waiver mechanism to focus on real issues

- > Vivado Incremental synthesis reduces compile time

- >> Reach out to your FAE for details/issues