# Vivado Design Suite Reference Guide

# Model-Based DSP Design Using System Generator

UG958 (v2020.2) November 18, 2020

# **Revision History**

The following table shows the revision history for this document.

| Section                               | Revision Summary                                                   |  |

|---------------------------------------|--------------------------------------------------------------------|--|

| 11/18/2020 Version 2020.2             |                                                                    |  |

| Xilinx Blockset                       | Clarification to DSPCPLX.                                          |  |

|                                       | Clarification to FIFO.                                             |  |

|                                       | Added DSP Macro 1.0. This replaces the deprecated DSP48 Macro 3.0. |  |

|                                       | Added DSP58.                                                       |  |

|                                       | Added Vitis HLS.                                                   |  |

| Xilinx SSR Blockset                   | Clarification to Vector DDFS.                                      |  |

| Chapter 4: System Generator Utilities | Clarification to xITBUtils.                                        |  |

| 06/03/2020 V                          | Version 2020.1                                                     |  |

| Xilinx Blockset                       | Clarifications to the following blocks:                            |  |

|                                       | Single-Port RAM                                                    |  |

|                                       | • ROM                                                              |  |

|                                       | Dual-Port RAM                                                      |  |

|                                       | AXI FIFO                                                           |  |

| Throughout document                   | Editorial updates.                                                 |  |

# **Table of Contents**

| Revision History                             |      |

|----------------------------------------------|------|

| Navigating Content by Design Process         |      |

|                                              |      |

| Chapter 1: Xilinx Blockset                   |      |

| Organization of Blockset Libraries           | g    |

| Common Options in Block Parameter Dialog Box | es26 |

| Block Reference Pages                        | 29   |

| Absolute                                     | 30   |

| Accumulator                                  | 31   |

| Addressable Shift Register                   | 33   |

| AddSub                                       | 35   |

| Assert                                       | 37   |

| AXI FIFO                                     | 40   |

| BitBasher                                    | 42   |

| Black Box                                    | 45   |

| CIC Compiler 4.0                             | 53   |

| Clock Enable Probe                           | 56   |

| Clock Probe                                  | 58   |

| CMult                                        | 59   |

| Complex Multiplier 6.0                       | 61   |

| Concat                                       | 64   |

| Constant                                     | 65   |

| Convert                                      | 67   |

| Convolution Encoder 9.0                      |      |

| CORDIC 6.0                                   | 73   |

| Counter                                      | 78   |

| DDS Compiler 6.0                             | 81   |

| Delay                                        | 88   |

| Depuncture                                   | 94   |

| Digital FIR Filter                           | 96   |

| Divide                                       | 99   |

| Divider Generator 5.1                        | 102  |

| Down Sample                    | .105  |

|--------------------------------|-------|

| DSP48E                         | .107  |

| DSP Macro 1.0                  | .113  |

| DSP48E1                        | .115  |

| DSP48E2                        | .122  |

| DSP58                          | .129  |

| DSPCPLX                        | . 136 |

| Dual Port RAM                  | . 144 |

| Exponential                    | . 148 |

| Expression                     | .150  |

| Fast Fourier Transform 9.1     | .151  |

| FDATool                        | .157  |

| FFT                            | . 158 |

| FIFO                           | .162  |

| FIR Compiler 7.2               | . 165 |

| Gateway In                     | . 173 |

| Gateway Out                    | . 177 |

| Indeterminate Probe            | . 180 |

| Interleaver/De-interleaver 8.0 | .180  |

| Inverse FFT                    | . 191 |

| Inverter                       | .195  |

| LFSR                           | .196  |

| Logical                        | 198   |

| MCode                          | 199   |

| ModelSim                       | . 225 |

| Mult                           | . 231 |

| MultAdd                        | . 233 |

| Mux                            | . 235 |

| Natural Logarithm              | 236   |

| Negate                         | . 238 |

| Opmode                         | 239   |

| Parallel to Serial             | .252  |

| Product                        | . 253 |

| Puncture                       | . 254 |

| Reciprocal                     | .255  |

| Reciprocal SquareRoot          |       |

| Reed-Solomon Decoder 9.0       |       |

| Reed-Solomon Encoder 9.0       | .265  |

| Regis   | ter                       | 271 |

|---------|---------------------------|-----|

| Reinte  | erpret                    | 272 |

| Relati  | ional                     | 273 |

| Requa   | antize                    | 274 |

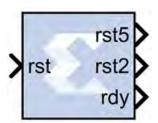

| Reset   | Generator                 | 276 |

| ROM.    |                           | 277 |

| Samp    | ole Time                  | 279 |

| Scale.  |                           | 280 |

| Serial  | l to Parallel             | 281 |

| Shift   |                           | 282 |

| Sine V  | Wave                      | 283 |

| Single  | e Port RAM                | 287 |

| Slice   |                           | 292 |

| Squar   | reRoot                    | 293 |

| Systei  | m Generator               | 294 |

| Thres   | shold                     | 300 |

| Time    | Division Demultiplexer    | 301 |

|         | Division Multiplexer      |     |

| Toolb   | par                       | 303 |

| Up Sa   | ample                     | 306 |

| =       | oi Decoder 9.1            |     |

| Vitis F | HLS                       | 314 |

|         |                           |     |

| Chapte  | er 2: Xilinx SSR Blockset | 317 |

| Scalar  | r2Vector                  | 317 |

| Vecto   | or Absolute               | 318 |

| Vecto   | or AddSub Fabric          | 319 |

| Vecto   | r Assert                  | 321 |

| Vecto   | r Complex Mult            | 323 |

| Vecto   | r Concat                  | 324 |

| Vecto   | r Constant                | 325 |

| Vecto   | r Convert                 | 326 |

| Vecto   | or DDFS                   | 329 |

| Vecto   | r Delay                   | 330 |

| Vecto   | or Delay Delta            | 333 |

| Vecto   | or Down Sample            | 333 |

|         | or FFT                    |     |

| Vecto   | or FIR                    | 338 |

| Vector Logical                                | 344 |

|-----------------------------------------------|-----|

| Vector Mux                                    | 345 |

| Vector Real Gateway In                        | 347 |

| Vector Real Gateway Out                       | 351 |

| Vector Real Mult                              | 354 |

| Vector Register                               | 357 |

| Vector Reinterpret                            | 358 |

| Vector Relational                             | 359 |

| Vector Slice                                  | 360 |

| Vector Up Sample                              | 362 |

| Vector2Scalar                                 | 364 |

| Chapter 3: Xilinx Reference Blockset          | 365 |

| Organization of Reference Blockset Libraries  | 365 |

| 2 Channel Decimate by 2 MAC FIR Filter        | 366 |

| 2n+1-tap Linear Phase MAC FIR Filter          | 368 |

| 2n-tap Linear Phase MAC FIR Filter            | 369 |

| 2n-tap MAC FIR Filter                         | 370 |

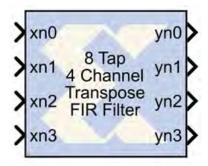

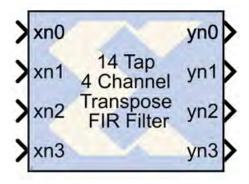

| 4-channel 8-tap Transpose FIR Filter          | 371 |

| 4n-tap MAC FIR Filter                         | 372 |

| 5x5Filter                                     | 373 |

| BPSK AWGN Channel                             | 375 |

| CIC Filter                                    | 376 |

| Convolutional Encoder                         | 378 |

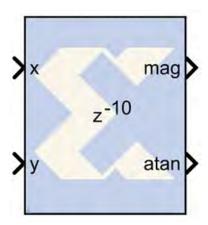

| CORDIC ATAN                                   | 381 |

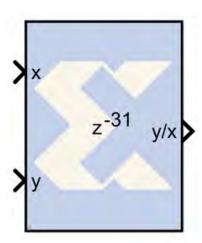

| CORDIC DIVIDER                                | 382 |

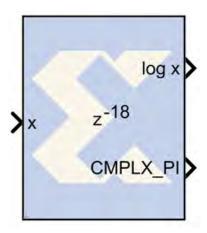

| CORDIC LOG                                    | 384 |

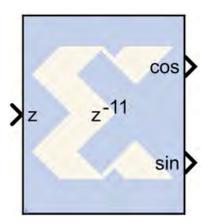

| CORDIC SINCOS                                 | 385 |

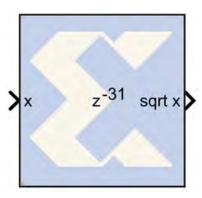

| CORDIC SQRT                                   | 387 |

| Dual Port Memory Interpolation MAC FIR Filter | 389 |

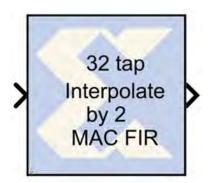

| Interpolation Filter                          | 390 |

| m-channel n-tap Transpose FIR Filter          | 391 |

| Mealy State Machine                           |     |

| Moore State Machine                           |     |

| n-tap Dual Port Memory MAC FIR Filter         | 399 |

| n-tap MAC FIR Filter                          |     |

| Registered Mealy State Machine                |     |

| Registered Moore State Machine                | 405 |

| Virtex Line Buffer                                                  | 409 |

|---------------------------------------------------------------------|-----|

| Virtex2 Line Buffer                                                 | 410 |

| Virtex2 5 Line Buffer                                               | 410 |

| White Gaussian Noise Generator                                      | 411 |

| Chapter 4: System Generator Utilities                               | 414 |

| xilinx.analyzer                                                     |     |

| xilinx.environment.getcachepath and xilinx.environment.setcachepath | 426 |

| xilinx.resource_analyzer                                            | 427 |

| xilinx.utilities.importBD                                           | 438 |

| xlAddTerms                                                          | 439 |

| xlConfigureSolver                                                   | 442 |

| xlfda_denominator                                                   | 443 |

| xlfda_numerator                                                     | 443 |

| xlGenerateButton                                                    | 444 |

| xlgetparam and xlsetparam                                           | 444 |

| xlgetparams                                                         | 446 |

| xlGetReOrderedCoeff                                                 | 447 |

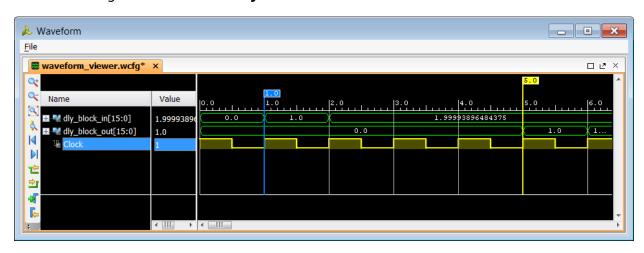

| xlOpenWaveFormData                                                  | 448 |

| xlSetUseHDL                                                         | 449 |

| xlTBUtils                                                           | 450 |

| Chapter 5: Programmatic Access                                      | 454 |

| System Generator API for Programmatic Generation                    |     |

| PG API Examples                                                     |     |

| PG API Error/Warning Handling and Messages                          | 467 |

| M-Code Access to Hardware Co-Simulation                             | 469 |

| Appendix A: Additional Resources and Legal Notices                  | 481 |

| Documentation Navigator and Design Hubs                             |     |

| References                                                          | 481 |

| Please Read: Important Legal Notices                                | 482 |

# Navigating Content by Design Process

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. This document covers the following design processes:

• Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, subsystem functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration.

# Xilinx Blockset

# **Organization of Blockset Libraries**

For convenience, this chapter is organized into the following sections.

| Organization of Blockset Libraries             | Describes how the Xilinx blocks are organized into libraries.                         |

|------------------------------------------------|---------------------------------------------------------------------------------------|

| Common Options in Block Parameter Dialog Boxes | Describes block parameters that are common to most blocks in the Xilinx blockset.     |

| Block Reference Pages                          | Alphabetical listing of the Xilinx blockset with detailed descriptions of each block. |

The Xilinx® Blockset contains building blocks for constructing DSP and other digital systems in FPGAs using Simulink®. The blocks are grouped into libraries according to their function, and some blocks with broad applicability (for example, the Gateway I/O blocks) are linked into multiple libraries. The following libraries are provided:

| Library               | Description                                                                                                                                                                                                                                                     |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

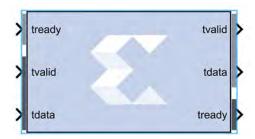

| AXI4 Blocks           | Includes every block that supports the AXI4 Interface.                                                                                                                                                                                                          |

| Basic Element Blocks  | Includes standard building blocks for digital logic.                                                                                                                                                                                                            |

| Communication Blocks  | Includes forward error correction and modulator blocks, commonly used in digital communications systems.                                                                                                                                                        |

| Control Logic Blocks  | Includes blocks for control circuitry and state machines.                                                                                                                                                                                                       |

| Data Type Blocks      | Includes blocks that convert data types (includes gateways).                                                                                                                                                                                                    |

| DSP Blocks            | Includes Digital Signal Processing (DSP) blocks.                                                                                                                                                                                                                |

| Floating-Point Blocks | Includes blocks that support the Floating-Point data type as well as other data types. Only a single data type is supported at a time. For example, a floating-point input produces a floating-point output; a fixed-point input produces a fixed-point output. |

| Index Blocks          | Includes all System Generator blocks.                                                                                                                                                                                                                           |

| Math Blocks           | Includes blocks that implement mathematical functions.                                                                                                                                                                                                          |

| Memory Blocks         | Includes blocks that implement and access memories.                                                                                                                                                                                                             |

| Tool Blocks           | Includes "Utility" blocks, e.g. code generation (System Generator token), resource estimation, HDL co-simulation, etc.                                                                                                                                          |

Each block has a background color that indicates the following:

| Background Color | Meaning                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Blue             | Block goes into the FPGA fabric and is free!                                                                    |

| Green            | Block goes into the FPGA fabric and is a Licensed Core. Go to the Xilinx web site to purchase the Core license. |

| Yellow           | Blocks on the boundary of your design like Gateway, Shared Memory Read,<br>Shared Memory Write, VDMA, etc.      |

| White            | Utility or Tool                                                                                                 |

| Red Symbol       | System Generator token (control panel).                                                                         |

### **AXI4 Blocks**

## Table 1: AXI4 Blocks

| AXI4 Block                     | Description                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

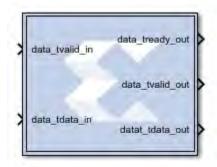

| AXI FIFO                       | The Xilinx® AXI FIFO block implements a FIFO memory queue with an AXI-compatible block interface.                                                                                                                                                                                                                                                             |

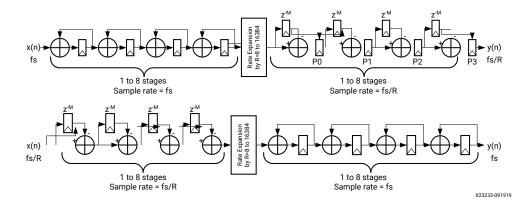

| CIC Compiler 4.0               | The Xilinx CIC Compiler provides the ability to design and implement AXI4-<br>Streamcompliant Cascaded Integrator-Comb (CIC) filters for a variety of Xilinx<br>FPGA devices.                                                                                                                                                                                 |

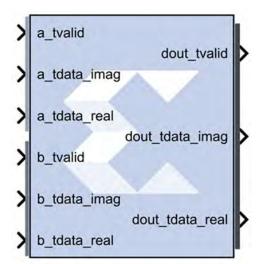

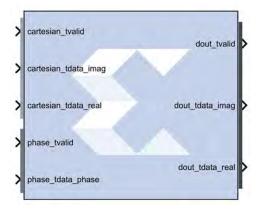

| Complex Multiplier 6.0         | The Complex Multiplier block implements AXI4-Stream compliant, high-<br>performance, optimized complex multipliers for devices based on user-specified<br>options.                                                                                                                                                                                            |

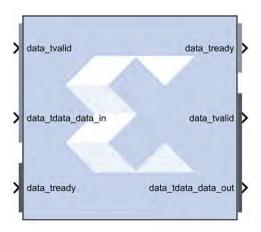

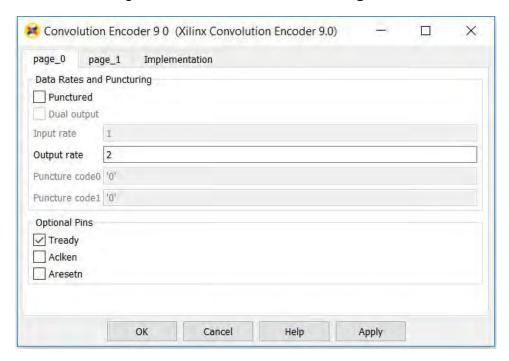

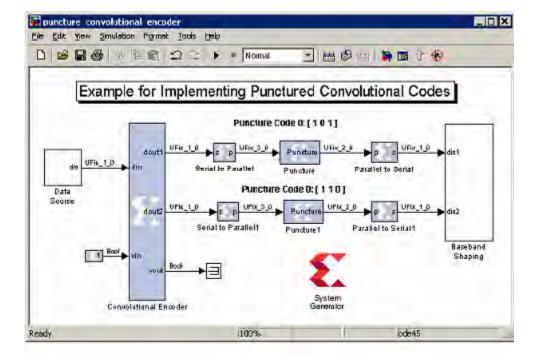

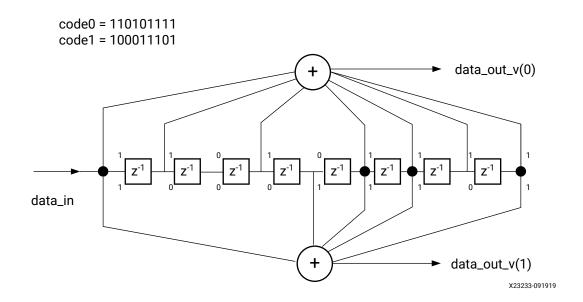

| Convolution Encoder 9.0        | The Xilinx Convolution Encoder block implements an encoder for convolution codes. Ordinarily used in tandem with a Viterbi decoder, this block performs forward error correction (FEC) in digital communication systems. This block adheres to the AMBA® AXI4-Stream standard.                                                                                |

| CORDIC 6.0                     | The Xilinx CORDIC block implements a generalized coordinate rotational digital computer (CORDIC) algorithm and is AXI compliant.                                                                                                                                                                                                                              |

| DDS Compiler 6.0               | The Xilinx DDS (Direct Digital Synthesizer) Compiler block implements high performance, optimized Phase Generation and Phase to Sinusoid circuits with AXI4-Stream compliant interfaces for supported devices.                                                                                                                                                |

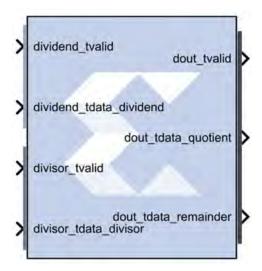

| Divider Generator 5.1          | The Xilinx Divider Generator block creates a circuit for integer division based on Radix-2 non-restoring division, or High-Radix division with prescaling.                                                                                                                                                                                                    |

| Fast Fourier Transform 9.1     | The Xilinx Fast Fourier Transform block implements the Cooley-Tukey FFT algorithm, a computationally efficient method for calculating the Discrete Fourier Transform (DFT). In addition, the block provides an AXI4-Stream-compliant interface.                                                                                                               |

| FIR Compiler 7.2               | This Xilinx FIR Compiler block provides users with a way to generate highly parameterizable, area-efficient, high-performance FIR filters with an AXI4-Stream-compliant interface.                                                                                                                                                                            |

| Interleaver/De-interleaver 8.0 | The Xilinx Interleaver Deinterleaver block implements an interleaver or a deinterleaver using an AXI4-compliant block interface. An interleaver is a device that rearranges the order of a sequence of input symbols. The term symbol is used to describe a collection of bits. In some applications, a symbol is a single bit. In others, a symbol is a bus. |

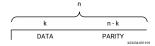

| Reed-Solomon Decoder 9.0       | The Reed-Solomon (RS) codes are block-based error correcting codes with a wide range of applications in digital communications and storage.                                                                                                                                                                                                                   |

| Reed-Solomon Encoder 9.0       | The Reed-Solomon (RS) codes are block-based error correcting codes with a wide range of applications in digital communications and storage. This block adheres to the AMBA® AXI4-Stream standard.                                                                                                                                                             |

| Viterbi Decoder 9.1            | Data encoded with a convolution encoder can be decoded using the Xilinx Viterbi decoder block. This block adheres to the AMBA® AXI4-Stream standard.                                                                                                                                                                                                          |

## **Basic Element Blocks**

**Table 2: Basic Element Blocks**

| Basic Element Block        | Description                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Absolute                   | The Xilinx Absolute block outputs the absolute value of the input.                                                                                                                                                                                                                                                                                          |

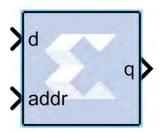

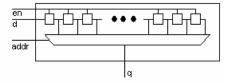

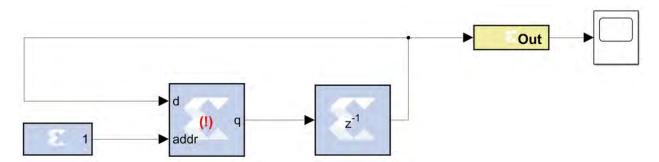

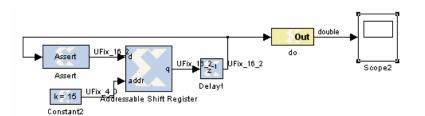

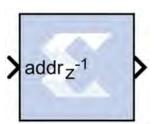

| Addressable Shift Register | The Xilinx Addressable Shift Register block is a variable-length shift register in which any register in the delay chain can be addressed and driven onto the output data port.                                                                                                                                                                             |

| Assert                     | The Xilinx Assert block is used to assert a rate and/or a type on a signal. This block has no cost in hardware and can be used to resolve rates and/or types in situations where designer intervention is required.                                                                                                                                         |

| BitBasher                  | The Xilinx BitBasher block performs slicing, concatenation, and augmentation of inputs attached to the block.                                                                                                                                                                                                                                               |

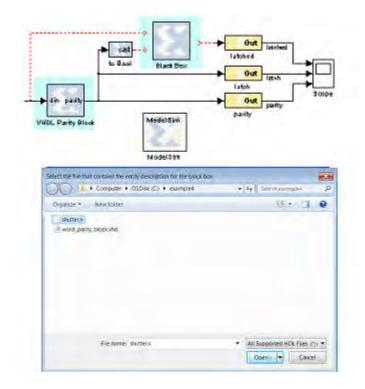

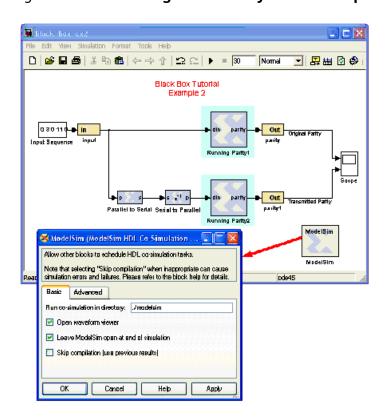

| Black Box                  | The System Generator Black Box block provides a way to incorporate hardware description language (HDL) models into System Generator.                                                                                                                                                                                                                        |

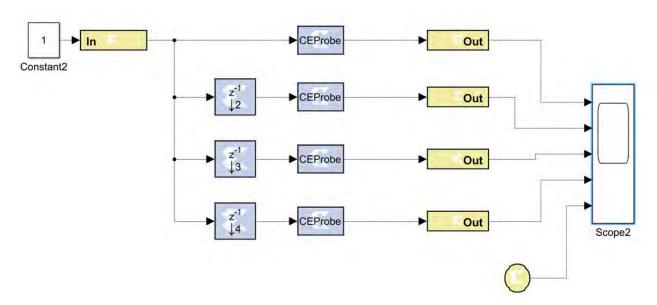

| Clock Enable Probe         | The Xilinx Clock Enable (CE) Probe provides a mechanism for extracting derived clock enable signals from Xilinx signals in System Generator models.                                                                                                                                                                                                         |

| Concat                     | The Xilinx Concat block performs a concatenation of n bit vectors represented by unsigned integer numbers, for example, n unsigned numbers with binary points at position zero.                                                                                                                                                                             |

| Constant                   | The Xilinx Constant block generates a constant that can be a fixed-point value, a Boolean value, or a DSP48 instruction. This block is similar to the SimulinkSimulink® constant block, but can be used to directly drive the inputs on Xilinx blocks.                                                                                                      |

| Convert                    | The Xilinx Convert block converts each input sample to a number of a desired arithmetic type. For example, a number can be converted to a signed (two's complement), or unsigned value.                                                                                                                                                                     |

| Counter                    | The Xilinx Counter block implements a free-running or count-limited type of an up, down, or up/down counter. The counter output can be specified as a signed or unsigned fixed-point number.                                                                                                                                                                |

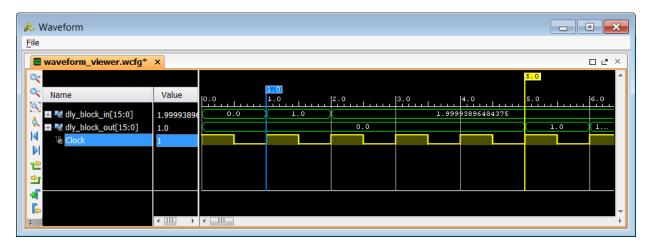

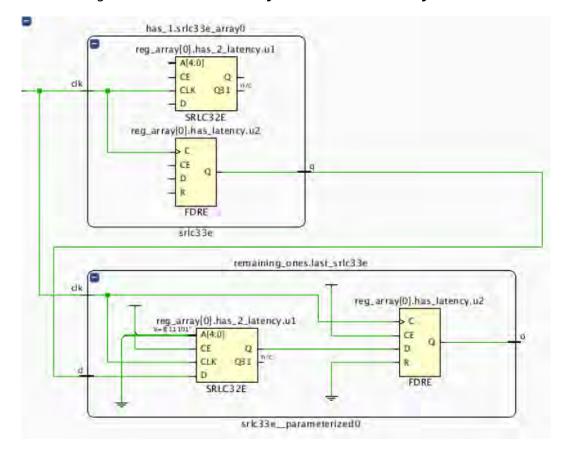

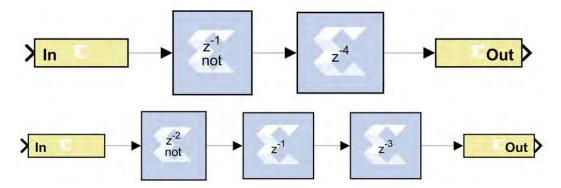

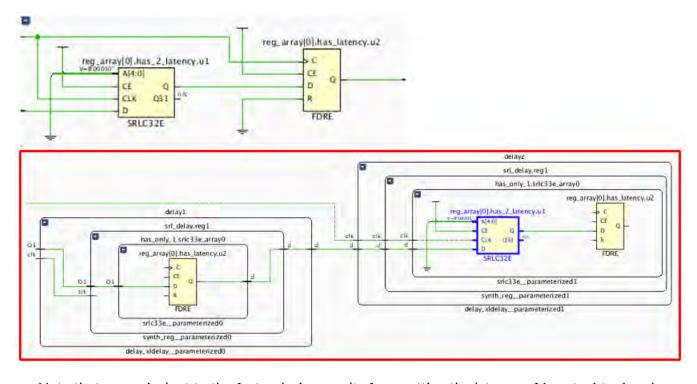

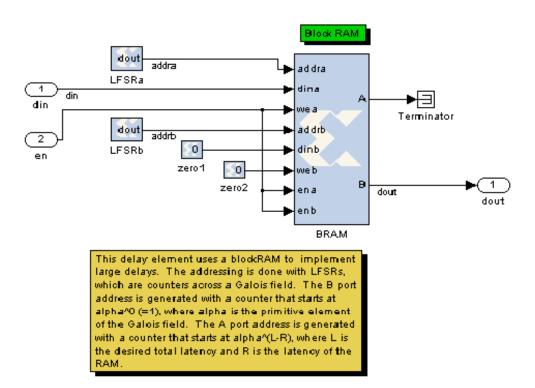

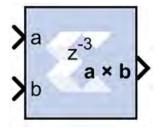

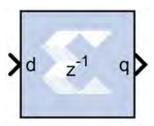

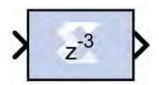

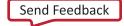

| Delay                      | The Xilinx Delay block implements a fixed delay of L cycles.                                                                                                                                                                                                                                                                                                |

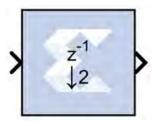

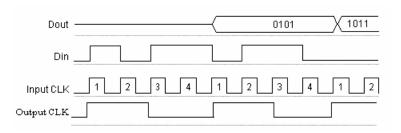

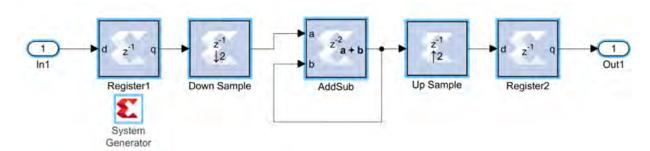

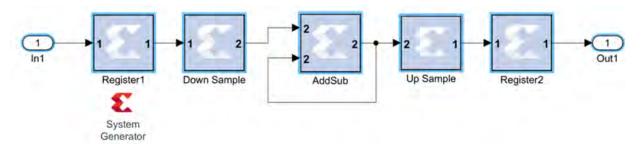

| Down Sample                | The Xilinx Down Sample block reduces the sample rate at the point where the block is placed in your design.                                                                                                                                                                                                                                                 |

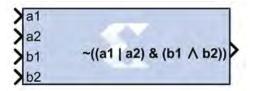

| Expression                 | The Xilinx Expression block performs a bitwise logical expression.                                                                                                                                                                                                                                                                                          |

| Gateway In                 | The Xilinx Gateway In blocks are the inputs into the Xilinx portion of your Simulink design. These blocks convert Simulink integer, double, and fixed-point data types into the System Generator fixed-point type. Each block defines a top-level input port or interface in the HDL design generated by System Generator.                                  |

| Gateway Out                | Xilinx Gateway Out blocks are the outputs from the Xilinx portion of your Simulink design. This block converts the System Generator fixed-point or floating-point data type into a Simulink integer, single, double, or fixed-point data type.                                                                                                              |

| Inverter                   | The Xilinx Inverter block calculates the bitwise logical complement of a fixed-point number. The block is implemented as a synthesizable VHDL module.                                                                                                                                                                                                       |

| LFSR                       | The Xilinx LFSR block implements a Linear Feedback Shift Register (LFSR). This block supports both the Galois and Fibonacci structures using either the XOR or XNOR gate and allows a re-loadable input to change the current value of the register at any time. The LFSR output and re-loadable input can be configured as either serial or parallel ports |

| Logical                    | The Xilinx Logical block performs bitwise logical operations on fixed-point numbers. Operands are zero padded and sign extended as necessary to make binary point positions coincide; then the logical operation is performed and the result is delivered at the output port.                                                                               |

Table 2: Basic Element Blocks (cont'd)

| Basic Element Block         | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

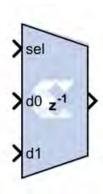

| Mux                         | The Xilinx Mux block implements a multiplexer. The block has one select input (type unsigned), and a user-configurable number of data bus inputs, ranging from 2 to 1024.                                                                                                                                                                                                                                                          |

| Parallel to Serial          | The Parallel to Serial block takes an input word and splits it into N time-multiplexed output words where N is the ratio of number of input bits to output bits. The order of the output can be either least significant bit first or most significant bit first.                                                                                                                                                                  |

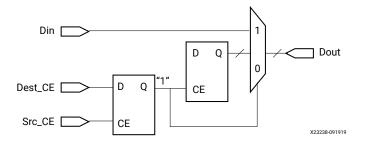

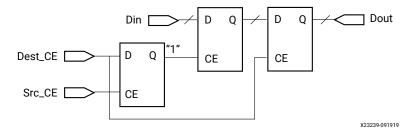

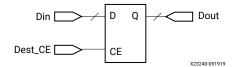

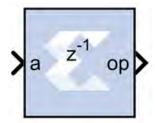

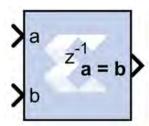

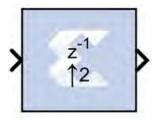

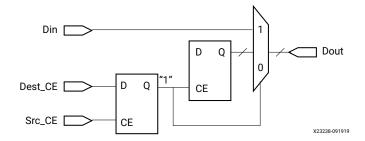

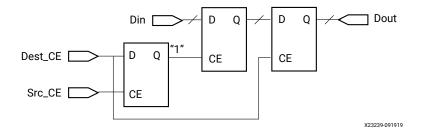

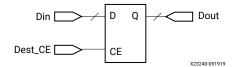

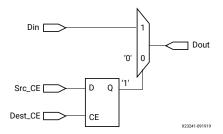

| Register                    | The Xilinx Register block models a D flip-flop-based register, having latency of one sample period.                                                                                                                                                                                                                                                                                                                                |

| Reinterpret                 | The Xilinx Reinterpret block forces its output to a new type without any regard for retaining the numerical value represented by the input.                                                                                                                                                                                                                                                                                        |

| Relational                  | The Xilinx Relational block implements a comparator.                                                                                                                                                                                                                                                                                                                                                                               |

| Requantize                  | The Xilinx Requantize block requantizes and scales its input signals.                                                                                                                                                                                                                                                                                                                                                              |

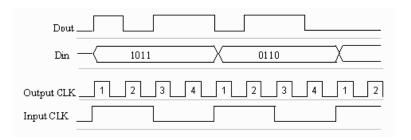

| Serial to Parallel          | The Serial to Parallel block takes a series of inputs of any size and creates a single output of a specified multiple of that size. The input series can be ordered either with the most significant word first or the least significant word first.                                                                                                                                                                               |

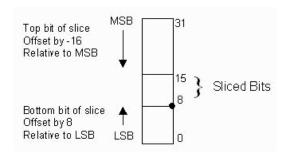

| Slice                       | The Xilinx Slice block allows you to slice off a sequence of bits from your input data and create a new data value. This value is presented as the output from the block. The output data type is unsigned with its binary point at zero.                                                                                                                                                                                          |

| System Generator            | The System Generator token serves as a control panel for controlling system and simulation parameters, and it is also used to invoke the code generator for netlisting. Every Simulink model containing any element from the Xilinx Blockset must contain at least one System Generator token. Once a System Generator token is added to a model, it is possible to specify how code generation, and simulation should be handled. |

| Threshold                   | The Xilinx Threshold block tests the sign of the input number. If the input number is negative, the output of the block is -1; otherwise, the output is 1. The output is a signed fixed-point integer that is 2 bits long. The block has one input and one output.                                                                                                                                                                 |

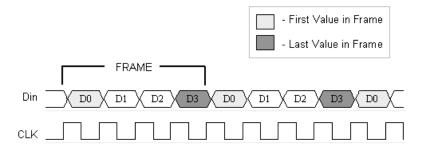

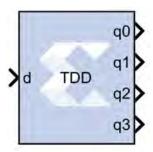

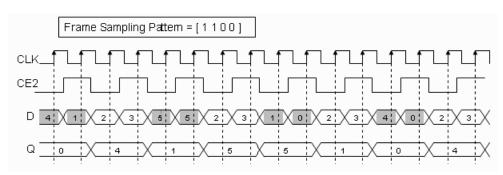

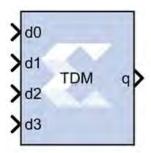

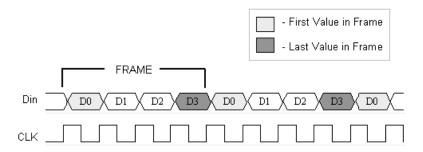

| Time Division Demultiplexer | The Xilinx Time Division Demultiplexer block accepts input serially and presents it to multiple outputs at a slower rate.                                                                                                                                                                                                                                                                                                          |

| Time Division Multiplexer   | The Xilinx Time Division Multiplexer block multiplexes values presented at input ports into a single faster rate output stream.                                                                                                                                                                                                                                                                                                    |

| Up Sample                   | The Xilinx Up Sample block increases the sample rate at the point where the block is placed in your design. The output sample period is I/n, where I is the input sample period, and n is the sampling rate.                                                                                                                                                                                                                       |

### **Communication Blocks**

**Table 3: Communication Blocks - FEC**

| Communication Block     | Description                                                                                                                                                                                                                                                                   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Convolution Encoder 9.0 | The Xilinx Convolution Encoder block implements an encoder for convolution codes. Ordinarily used in tandem with a Viterbi decoder, this block performs forward error correction (FEC) in digital communication systems. This block adheres to the AMBA AXI4-Stream standard. |

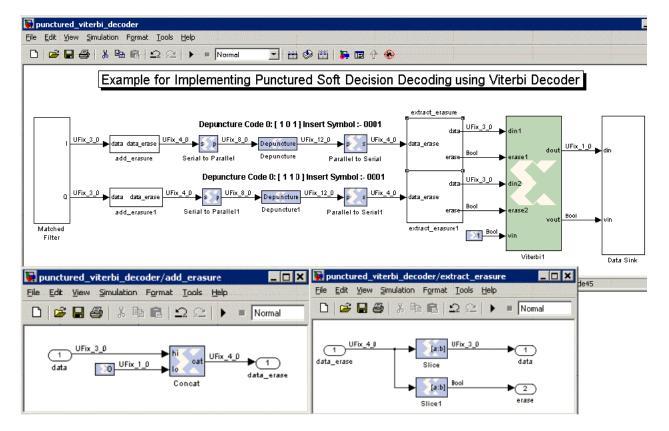

| Depuncture              | The Xilinx Depuncture block allows you to insert an arbitrary symbol into your input data at the location specified by the depuncture code.                                                                                                                                   |

Table 3: Communication Blocks - FEC (cont'd)

| Communication Block            | Description                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interleaver/De-interleaver 8.0 | The Xilinx Interleaver Deinterleaver block implements an interleaver or a deinterleaver using an AXI4-compliant block interface. An interleaver is a device that rearranges the order of a sequence of input symbols. The term symbol is used to describe a collection of bits. In some applications, a symbol is a single bit. In others, a symbol is a bus. |

| Puncture                       | The Xilinx Puncture block removes a set of user-specified bits from the input words of its data stream.                                                                                                                                                                                                                                                       |

| Reed-Solomon Decoder 9.0       | The Reed-Solomon (RS) codes are block-based error correcting codes with a wide range of applications in digital communications and storage. This block adheres to the AMBA AXI4-Stream standard.                                                                                                                                                              |

| Reed-Solomon Encoder 9.0       | The Reed-Solomon (RS) codes are block-based error correcting codes with a wide range of applications in digital communications and storage. This block adheres to the AMBA AXI4-Stream standard.                                                                                                                                                              |

| Viterbi Decoder 9.1            | Data encoded with a convolution encoder can be decoded using the Xilinx Viterbi decoder block. This block adheres to the AMBA AXI4-Stream standard.                                                                                                                                                                                                           |

## **Control Logic Blocks**

**Table 4: Control Logic Blocks**

| Control Logic Block | Description                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI FIFO            | The Xilinx AXI FIFO block implements a FIFO memory queue with an AXI-compatible block interface.                                                                                                                                                                                                                                                                     |

| Black Box           | The System Generator Black Box block provides a way to incorporate hardware description language (HDL) models into System Generator.                                                                                                                                                                                                                                 |

| Constant            | The Xilinx Constant block generates a constant that can be a fixed-point value, a Boolean value, or a DSP48 instruction. This block is similar to the Simulink constant block, but can be used to directly drive the inputs on Xilinx blocks.                                                                                                                        |

| Counter             | The Xilinx Counter block implements a free-running or count-limited type of an up, down, or up/down counter. The counter output can be specified as a signed or unsigned fixed-point number.                                                                                                                                                                         |

| Dual Port RAM       | The Xilinx Dual Port RAM block implements a random access memory (RAM). Dual ports enable simultaneous access to the memory space at different sample rates using multiple data widths.                                                                                                                                                                              |

| Expression          | The Xilinx Expression block performs a bitwise logical expression.                                                                                                                                                                                                                                                                                                   |

| FIFO                | The Xilinx FIFO block implements an FIFO memory queue.                                                                                                                                                                                                                                                                                                               |

| Inverter            | The Xilinx Inverter block calculates the bitwise logical complement of a fixed-point number. The block is implemented as a synthesizable VHDL module.                                                                                                                                                                                                                |

| Logical             | The Xilinx Logical block performs bitwise logical operations on fixed-point numbers. Operands are zero padded and sign extended as necessary to make binary point positions coincide; then the logical operation is performed and the result is delivered at the output port.                                                                                        |

| MCode               | The Xilinx MCode block is a container for executing a user-supplied MATLAB® function within Simulink. A parameter on the block specifies the M-function name. The block executes the M-code to calculate block outputs during a simulation. The same code is translated in a straightforward way into equivalent behavioral VHDL/Verilog when hardware is generated. |

| Mux                 | The Xilinx Mux block implements a multiplexer. The block has one select input (type unsigned) and a user-configurable number of data bus inputs, ranging from 2 to 1024.                                                                                                                                                                                             |

Table 4: Control Logic Blocks (cont'd)

| Control Logic Block | Description                                                                                                                                                                                                                        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register            | The Xilinx Register block models a D flip-flop-based register, having latency of one sample period.                                                                                                                                |

| Relational          | The Xilinx Relational block implements a comparator.                                                                                                                                                                               |

| ROM                 | The Xilinx ROM block is a single port read-only memory (ROM).                                                                                                                                                                      |

| Shift               | The Xilinx Shift block performs a left or right shift on the input signal. The result will have the same fixed-point container as that of the input.                                                                               |

| Single Port RAM     | The Xilinx Single Port RAM block implements a random access memory (RAM) with one data input and one data output port.                                                                                                             |

| Slice               | The Slice block allows you to slice off a sequence of bits from your input data and create a new data value. This value is presented as the output from the block. The output data type is unsigned with its binary point at zero. |

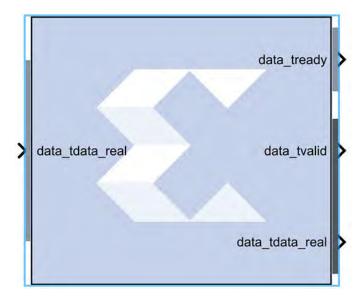

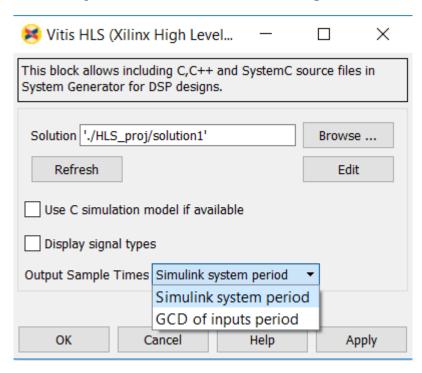

| Vitis HLS           | The Xilinx Vitis™ HLS block allows the functionality of a design to be included in a System Generator design. The Vitis HLS design can include C, C++, and System C design sources.                                                |

## **Data Type Blocks**

**Table 5: Data Type Blocks**

| Data Type Block    | Description                                                                                                                                                                                                                                                                                                                |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BitBasher          | The Xilinx BitBasher block performs slicing, concatenation, and augmentation of inputs attached to the block.                                                                                                                                                                                                              |

| Concat             | The Xilinx Concat block performs a concatenation of n bit vectors represented by unsigned integer numbers, for example, n unsigned numbers with binary points at position zero.                                                                                                                                            |

| Convert            | The Xilinx Convert block converts each input sample to a number of a desired arithmetic type. For example, a number can be converted to a signed (two's complement), or unsigned value.                                                                                                                                    |

| Gateway In         | The Xilinx Gateway In blocks are the inputs into the Xilinx portion of your Simulink design. These blocks convert Simulink integer, double, and fixed-point data types into the System Generator fixed-point type. Each block defines a top-level input port or interface in the HDL design generated by System Generator. |

| Gateway Out        | Xilinx Gateway Out blocks are the outputs from the Xilinx portion of your Simulink design. This block converts the System Generator fixed-point, or floating-point data type into a Simulink integer, single, double, or fixed-point data type.                                                                            |

| Parallel to Serial | The Parallel to Serial block takes an input word and splits it into N time-multiplexed output words where N is the ratio of number of input bits to output bits. The order of the output can be either least significant bit first or most significant bit first.                                                          |

| Reinterpret        | The Xilinx Reinterpret block forces its output to a new type without any regard for retaining the numerical value represented by the input.                                                                                                                                                                                |

| Requantize         | The Xilinx Requantize block requantizes and scales its input signals.                                                                                                                                                                                                                                                      |

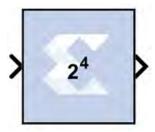

| Scale              | The Xilinx Scale block scales its input by a power of two. The power can be either positive or negative. The block has one input and one output. The scale operation has the effect of moving the binary point without changing the bits in the container                                                                  |

| Serial to Parallel | The Serial to Parallel block takes a series of inputs of any size and creates a single output of a specified multiple of that size. The input series can be ordered either with the most significant word first or the least significant word first.                                                                       |

Table 5: Data Type Blocks (cont'd)

| Data Type Block | Description                                                                                                                                                                                                                                                        |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift           | The Xilinx Shift block performs a left or right shift on the input signal. The result will have the same fixed-point container as that of the input.                                                                                                               |

| Slice           | The Xilinx Slice block allows you to slice off a sequence of bits from your input data and create a new data value. This value is presented as the output from the block. The output data type is unsigned with its binary point at zero.                          |

| Threshold       | The Xilinx Threshold block tests the sign of the input number. If the input number is negative, the output of the block is -1; otherwise, the output is 1. The output is a signed fixed-point integer that is 2 bits long. The block has one input and one output. |

#### **DSP Blocks**

#### Table 6: **DSP Blocks**

| DSP Block              | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CIC Compiler 4.0       | The Xilinx CIC Compiler provides the ability to design and implement AXI4-<br>Stream-compliant Cascaded Integrator-Comb (CIC) filters for a variety of Xilinx<br>FPGA devices.                                                                                                                                                                                                                                                            |

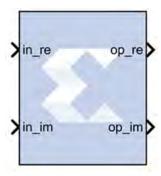

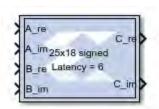

| Complex Multiplier 6.0 | The Complex Multiplier block implements AXI4-Stream compliant, high-performance, optimized complex multipliers for devices based on user-specified options.                                                                                                                                                                                                                                                                               |

| CORDIC 6.0             | The Xilinx CORDIC block implements a generalized coordinate rotational digital computer (CORDIC) algorithm and is AXI compliant.                                                                                                                                                                                                                                                                                                          |

| DDS Compiler 6.0       | The Xilinx DDS (Direct Digital Synthesizer) Compiler block implements high performance, optimized Phase Generation, and Phase to Sinusoid circuits with AXI4-Stream compliant interfaces for supported devices.                                                                                                                                                                                                                           |

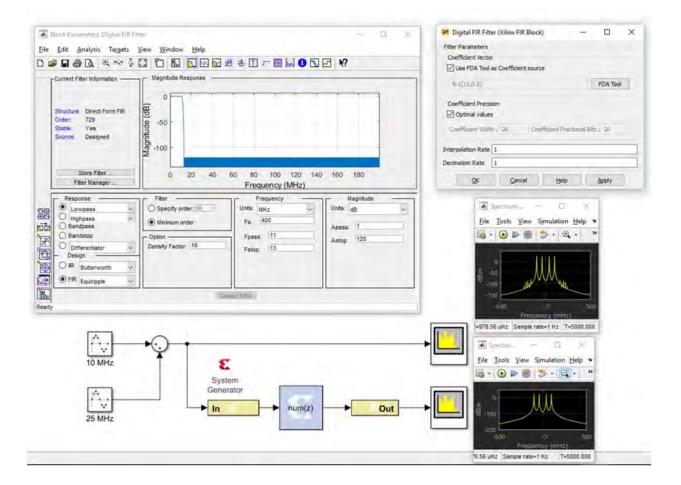

| Digital FIR Filter     | The Xilinx Digital FIR Filter block allows you to generate highly parameterizable, area-efficient, high-performance single channel FIR filters.                                                                                                                                                                                                                                                                                           |

| Divider Generator 5.1  | The Xilinx Divider Generator block creates a circuit for integer division based on Radix-2 non-restoring division, or High-Radix division with prescaling.                                                                                                                                                                                                                                                                                |

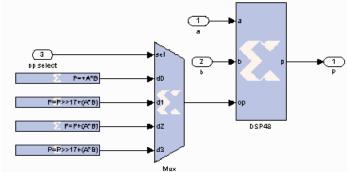

| DSP Macro 1.0          | The System Generator DSP macro block provides a device independent abstraction of the DSP48E1, DSP48E2, and DSP58 blocks. Using this block instead of using a technology-specific DSP slice helps makes the design more portable between Xilinx technologies.                                                                                                                                                                             |

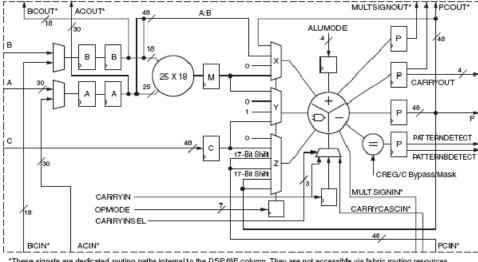

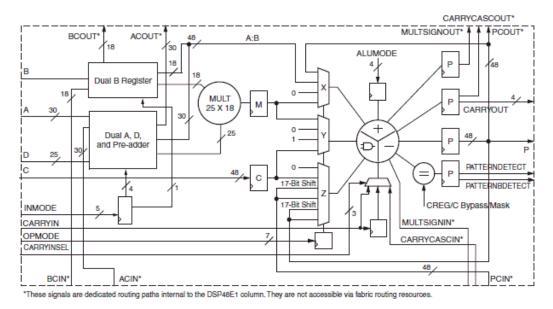

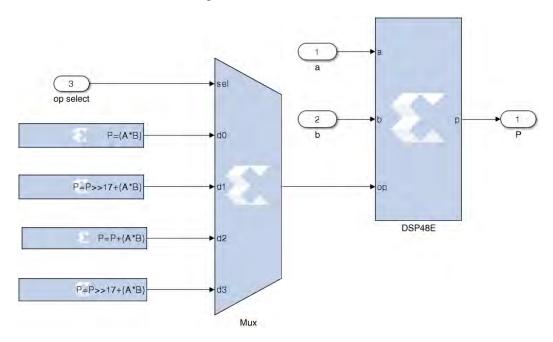

| DSP48E                 | The Xilinx DSP48E block is an efficient building block for DSP applications that use supported devices. The DSP48E combines an 18-bit by 25-bit signed multiplier with a 48-bit adder and programmable mux to select the adder's input.                                                                                                                                                                                                   |

| DSP48E1                | The Xilinx DSP48E1 block is an efficient building block for DSP applications that use 7 series devices. Enhancements to the DSP48E1 slice provide improved flexibility and utilization, improved efficiency of applications, reduced overall power consumption, and increased maximum frequency. The high performance allows designers to implement multiple slower operations in a single DSP48E1 slice using time-multiplexing methods. |

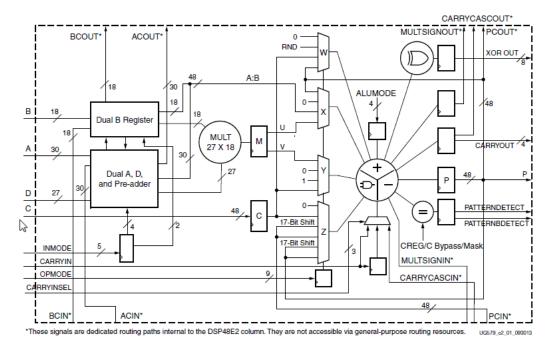

| DSP48E2                | The Xilinx DSP48E2 block is an efficient building block for DSP applications that use UltraScale™ devices. DSP applications use many binary multipliers and accumulators that are best implemented in dedicated DSP resources. UltraScale™ devices have many dedicated low-power DSP slices, combining high speed with small size while retaining system design flexibility.                                                              |

Table 6: **DSP Blocks** (cont'd)

| DSP Block                  | Description                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

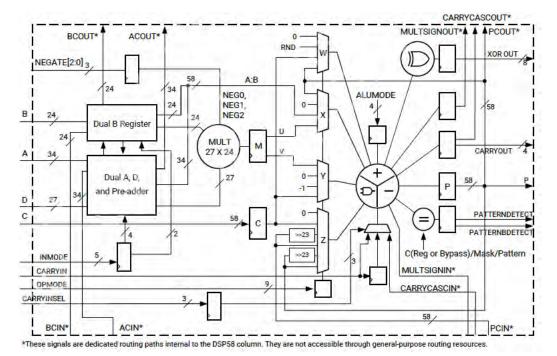

| DSP58                      | The Xilinx DSP58 block is an efficient building block for DSP applications that use Versal™ devices. DSP applications use many binary multipliers and accumulators that are best implemented in dedicated DSP resources. Versal™ devices have many dedicated low-power DSP slices, combining high speed with small size while retaining system design flexibility. |

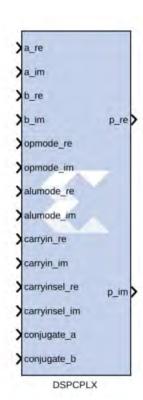

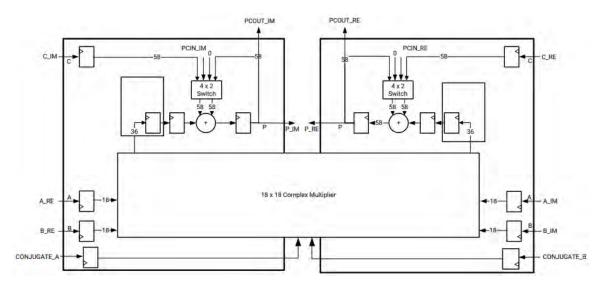

| DSPCPLX                    | The Xilinx DSPCPLX block is one of the advanced features provided by Versal™ architecture DSP, which is the optimized solution to deal with 18x18 complex multiplication followed by 58 + 58 accumulation operation.                                                                                                                                               |

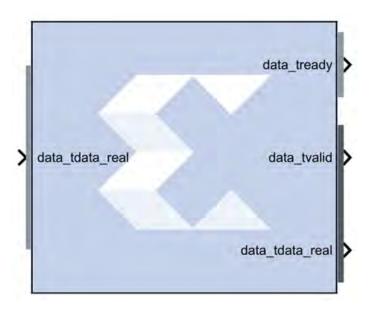

| Fast Fourier Transform 9.1 | The Xilinx Fast Fourier Transform block implements the Cooley-Tukey FFT algorithm, a computationally efficient method for calculating the Discrete Fourier Transform (DFT). In addition, the block provides an AXI4-Stream-compliant interface.                                                                                                                    |

| FDATool                    | The Xilinx FDATool block provides an interface to the FDATool software available as part of the MATLAB Signal Processing Toolbox.                                                                                                                                                                                                                                  |

| FFT                        | The Xilinx FFT (Fast Fourier Transform) block takes a block of time domain waveform data and computes the frequency of the sinusoid signals that make up the waveform.                                                                                                                                                                                             |

| FIR Compiler 7.2           | This Xilinx FIR Compiler block provides users with a way to generate highly parameterizable, area-efficient, high-performance FIR filters with an AXI4-Stream-compliant interface.                                                                                                                                                                                 |

| Inverse FFT                | The Xilinx Inverse FFT block performs a fast inverse (or backward) Fourier transform (IDFT), which undoes the process of Discrete Fourier Transform (DFT). The Inverse FFT maps the signal back from the frequency domain into the time domain.                                                                                                                    |

| LFSR                       | The Xilinx LFSR block implements a Linear Feedback Shift Register (LFSR). This block supports both the Galois and Fibonacci structures using either the XOR or XNOR gate and allows a re-loadable input to change the current value of the register at any time. The LFSR output and re-loadable input can be configured as either serial or parallel ports        |

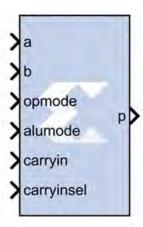

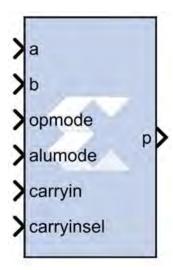

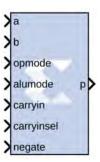

| Opmode                     | The Xilinx Opmode block generates a constant that is a DSP48E, DSP48E1, or DSP48E2 instruction. It is is a 15-bit instruction for DSP48E, a 20-bit instruction for DSP48E1, and a 22-bit instruction for DSP48E2. The instruction consists of the opmode, carry-in, carry-in select, alumode, and (for DSP48E1 and DSP48E2) the inmode bits.                       |

| Product                    | The Xilinx Product block implements a scalar or complex multiplier. It computes the product of the data on its two input channels, producing the result on its output channel. For complex multiplication the input and output have two components: real and imaginary.                                                                                            |

| Sine Wave                  | The Xilinx Sine Wave block generates a sine wave, using simulation time as the time source.                                                                                                                                                                                                                                                                        |

### **Floating-Point Blocks**

The blocks in this library support the Floating-Point data type as well as other data types. Only a single data type is supported at a time. For example, a floating-point input produces a floating-point output; a fixed-point input produces a fixed-point output.

**Table 7: Floating-Point Blocks**

| Floating-Point Block | Description                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------|

| AXI FIFO             | The Xilinx AXI FIFO block a FIFO memory queue with an AXI-compatible block interfimplementsace. |

Table 7: Floating-Point Blocks (cont'd)

| Floating-Point Block       | Description                                                                                                                                                                                                                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Absolute                   | The Xilinx Absolute block outputs the absolute value of the input.                                                                                                                                                                                                                                                         |

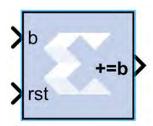

| Accumulator                | The Xilinx Accumulator block implements an adder or subtractor-based scaling accumulator.                                                                                                                                                                                                                                  |

| Addressable Shift Register | The Xilinx Addressable Shift Register block is a variable-length shift register in which any register in the delay chain can be addressed and driven onto the output data port.                                                                                                                                            |

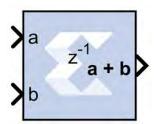

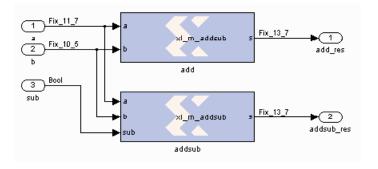

| AddSub                     | The Xilinx AddSub block implements an adder/subtractor. The operation can be fixed (Addition or Subtraction) or changed dynamically under control of the sub mode signal.                                                                                                                                                  |

| Assert                     | The Xilinx Assert block is used to assert a rate and/or a type on a signal. This block has no cost in hardware and can be used to resolve rates and/or types in situations where designer intervention is required.                                                                                                        |

| Black Box                  | The System Generator Black Box block provides a way to incorporate hardware description language (HDL) models into System Generator.                                                                                                                                                                                       |

| CMult                      | The Xilinx CMult block implements a gain operator, with output equal to the product of its input by a constant value. This value can be a MATLAB expression that evaluates to a constant.                                                                                                                                  |

| Constant                   | The Xilinx Constant block generates a constant that can be a fixed-point value, a Boolean value, or a DSP48 instruction. This block is similar to the Simulink constant block, but can be used to directly drive the inputs on Xilinx blocks.                                                                              |

| Convert                    | The Xilinx Convert block converts each input sample to a number of a desired arithmetic type. For example, a number can be converted to a signed (two's complement), or unsigned value.                                                                                                                                    |

| Delay                      | The Xilinx Delay block implements a fixed delay of L cycles.                                                                                                                                                                                                                                                               |

| Divide                     | The Xilinx Divide block performs both fixed-point and floating-point division with the a input being the dividend and the b input the divisor. Both inputs must be of the same data type.                                                                                                                                  |

| Dual Port RAM              | The Xilinx Dual Port RAM block implements a random access memory (RAM). Dual ports enable simultaneous access to the memory space at different sample rates using multiple data widths.                                                                                                                                    |

| Exponential                | This Xilinx Exponential block preforms the exponential operation on the input. Currently, only the floating-point data type is supported.                                                                                                                                                                                  |

| Fast Fourier Transform 9.1 | The Xilinx Fast Fourier Transform block implements the Cooley-Tukey FFT algorithm, a computationally efficient method for calculating the Discrete Fourier Transform (DFT). In addition, the block provides an AXI4-Stream-compliant interface.                                                                            |

| FFT                        | The Xilinx FFT (Fast Fourier Transform) block takes a block of time domain waveform data and computes the frequency of the sinusoid signals that make up the waveform.                                                                                                                                                     |

| FIFO                       | The Xilinx FIFO block implements an FIFO memory queue.                                                                                                                                                                                                                                                                     |

| Gateway In                 | The Xilinx Gateway In blocks are the inputs into the Xilinx portion of your Simulink design. These blocks convert Simulink integer, double, and fixed-point data types into the System Generator fixed-point type. Each block defines a top-level input port or interface in the HDL design generated by System Generator. |

| Gateway Out                | Xilinx Gateway Out blocks are the outputs from the Xilinx portion of your Simulink design. This block converts the System Generator fixed-point or floating-point data type into a Simulink integer, single, double, or fixed-point data type.                                                                             |

| Inverse FFT                | The Xilinx Inverse FFT block performs a fast inverse (or backward) Fourier transform (IDFT), which undoes the process of Discrete Fourier Transform (DFT). The Inverse FFT maps the signal back from the frequency domain into the time domain.                                                                            |

Table 7: Floating-Point Blocks (cont'd)

| Floating-Point Block  | Description                                                                                                                                                                                  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mult                  | The Xilinx Mult block implements a multiplier. It computes the product of the data on its two input ports, producing the result on its output port.                                          |

| MultAdd               | The Xilinx MultAdd block performs both fixed-point and floating-point multiply and addition with the a and b inputs used for the multiplication and the c input for addition or subtraction. |

| Mux                   | The Xilinx                                                                                                                                                                                   |

| Natural Logarithm     | The Xilinx Mux block implements a multiplexer. Natural Logarithm block produces the natural logarithm of the input.                                                                          |

| Negate                | The Xilinx Negate block computes the arithmetic negation of its input.                                                                                                                       |

| Reciprocal            | The Xilinx Reciprocal block performs the reciprocal on the input. Currently, only the floating-point data type is supported.                                                                 |

| Reciprocal SquareRoot | The Xilinx Reciprocal SquareRoot block performs the reciprocal squareroot on the input. Currently, only the floating-point data type is supported.                                           |

| Register              | The Xilinx Register block models a D flip-flop-based register, having latency of one sample period.                                                                                          |

| Reinterpret           | The Xilinx Reinterpret block forces its output to a new type without any regard for retaining the numerical value represented by the input.                                                  |

| Relational            | The Xilinx Relational block implements a comparator.                                                                                                                                         |

| ROM                   | The Xilinx ROM block is a single port read-only memory (ROM).                                                                                                                                |

| Single Port RAM       | The Xilinx Single Port RAM block implements a random access memory (RAM) with one data input and one data output port.                                                                       |

| SquareRoot            | The Xilinx SquareRoot block performs the square root on the input. Currently, only the floating-point data type is supported.                                                                |

#### **Index Blocks**

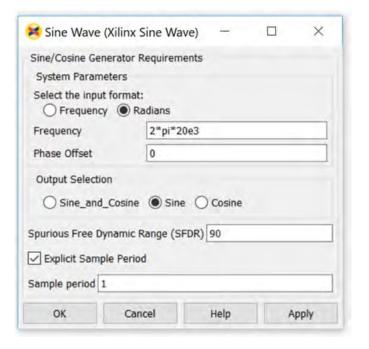

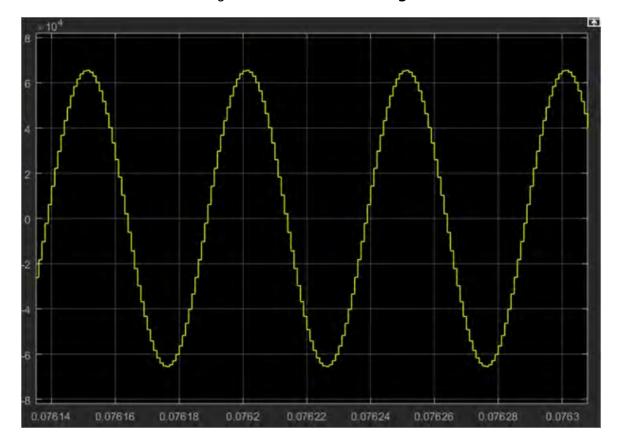

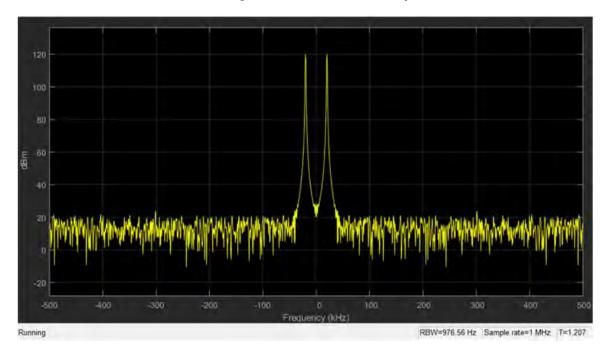

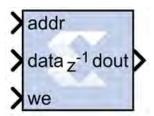

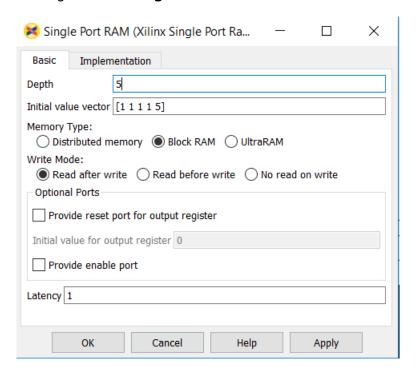

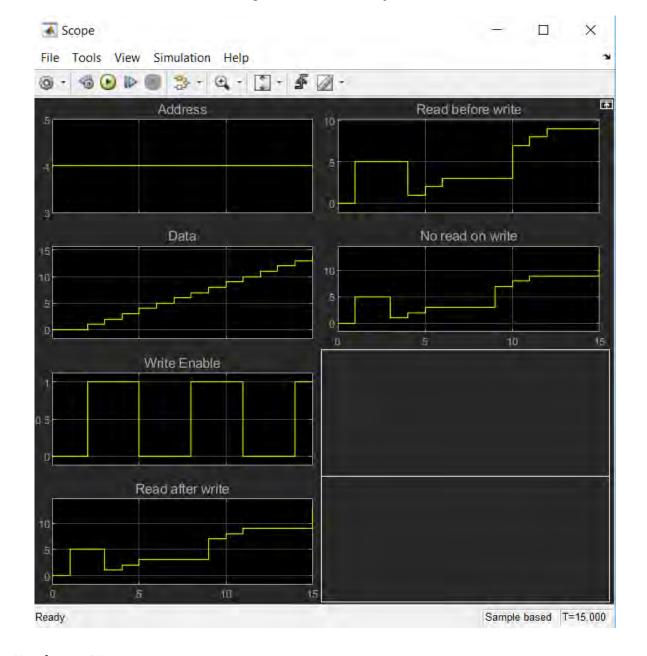

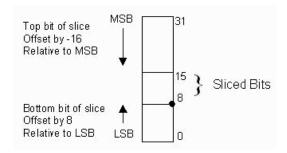

**Table 8: Index Blocks**