Automotive Grade Zynq 7000 SoCs

- Devices

- SoCs, MPSoCs and RFSoCs

- Automotive-grade XA Zynq 7000 SoCs

Design Confidently

AMD takes our commitment to long lifecycles very seriously. We are pleased to announce that support is formally being extended for all 7 series devices until at least 2035. This includes all speed and temperature grades for Spartan™ 7, Artix™ 7, Kintex™ 7, and Virtex™ 7 FPGAs, as well as Zynq™ 7000 SoCs.

Automotive Grade Zynq 7000 SoC Product Advantages

Automotive grade (XA) Zynq™ 7000 SoCs are ideally suited to the high computation requirements of advanced driver assistance systems (ADAS). The combined programmability of hardware and software allows development teams to integrate a complete ADAS imaging flow, from sensing through environmental characterization to feature implementation into a single device. Also, functions can be moved between hardware and software to eliminate data flow bottlenecks, maximize performance and minimize resources. The XA Zynq 7000 SoC devices with their architecturally inherent flexibility provide a cost-effective solution for building highly scalable platforms allowing system designers to dramatically reduce development times.

| Value | Features |

|---|---|

| Programmable System Integration |

|

| Increased System Performance |

|

| BOM Cost Reduction |

|

| Total Power Reduction |

|

| Accelerated Design Productivity |

|

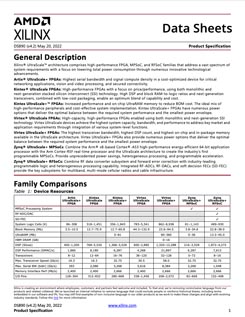

Processing System (PS)

| Features | All Devices |

|---|---|

| Processor Core | Dual Arm® Cortex®-A9 MPCore™ with CoreSight™ technology |

| Processor Extensions | NEON & Single/Double Precision Floating Point for each processor |

| Maximum Frequency/Processor | 667 MHz (-1) |

| L1 Cache | 32 KB Instruction, 32 KB Data per processor |

| L2 Cache | 512 KB |

| On-Chip Memory | 256 KB |

| External Memory Support | DDR3L, DDR3, DDR2, LPDDR2 |

| External Static Memory Support | 2x Quad-SPI, NAND, NOR |

| DMA Channels | 8 (4 dedicated to Programmable Logic) |

| Peripherals | 2x UART, 2x CAN 2.0B, 2x I2C, 2x SPI, 4x 32b GPIO |

| Peripherals w/ built-in DMA | 2x USB 2.0 (OTG), 2x Tri-mode Gigabit Ethernet, 2x SD/SDIO |

| Security | AES and SHA 256b for device security |

Programmable Logic

| XA7Z010 | XA7Z020 | XA7Z030 | |

| AMD 7 Series Programmable Logic Equivalent | Artix™ 7 FPGA | Artix™ 7 FPGA | Kintex™ 7 FPGA |

| Programmable Logic Cells | 28K Logic Cells (~430K) | 85K Logic Cells (~1.3M) | 125K Logic Cells (~1.9M) |

| Look-Up Tables (LUTs) | 17,600 | 53,200 | 78,600 |

| Flip-Flops | 35,200 | 106,400 | 157,200 |

| Extensible BlockRAM (# 36 Kb Blocks) | 240 KB (60) | 560 KB (140) | 1,060 KB (265) |

| Programmable DSP Slices (18x25 MACCs) | 80 | 220 | 400 |

| PCI Express (Root Complex and Endpoint) | - | - | Gen2 x4 |

| Maximums I/O Pins (PL only) | 100 | 200 | 163 (+ 4 GTX) |

Note: Some restrictions may apply. Refer to UG585, Zynq 7000 SoC Technical Reference Manual and DS188, XA Zynq 7000 SoC Overview for details.